# Switching Power Converter System

#### **Field of the Invention**

5

10

15

20

25

30

35

The invention relates to a switching power converter system, and more specifically to a crosswise switching charge pump setting capable of transferring and summating electrical charge for generating a summated positive as well as negative switched voltage alternately with respect to a reference voltage and in particular applicable for generating a switching high voltage signal being pulse-width-modulated (PWM) in response to a control signal.

# **Description of Related and Prior Art**

In general the semiconductor industry has made great progress in the last decennia's, however despite the great progress, it is still not possible to provide for example a half bridge switching power setting comprising only two series connected and counter phase driven semiconductors (MOSFET, IGBT, BJT) being operable to generate a switching output voltage of several kilovolts in combination with a high operational switching frequency as well as fast transition times.

In addition, it is to be noted that with an increase of switching output voltage at an output of the half bridge switching power setting (not shown) comprising only two semiconductors connected in series, a cross-current flow through the semiconductors during each transition will increase as well due to an output capacitance resided in each constituted semiconductor with a consequence of a more or less exponential increase of switching losses in the half bridge switching power setting with a linear increase of switching output voltage.

In general in order to implement a half bridge or full bridge switching power setting operable to generate a switching output voltage of several kilovolts, several semiconductors may be connected in series splitting the switching output voltage into an applicable blocking voltage being equally divided across each semiconductor and consequently splitting the total loss in the constituted semiconductors as well, as will be well understood by those skilled in the art. In addition, it is to be noted that with the series connection of several semiconductors as described above the output capacitance resided in each constituted semiconductor will be series connected as well achieving by means of the series connection a decreased overall output capacitance obtaining reduced switching losses as well as reduced transition times. However tolerance of the

10

15

20

25

30

35

constituted components may introduce divergent switching behaviour for each semiconductor taken alone resulting in reduced reliability as well as disturbed behaviour.

In order to overcome these deficiencies to a greater or lesser extent a network of diodes and capacitors may be implemented in a manner as shown for example in reference document "Voltage Sag Restorer with Diode-Clamped Multilevel Bridge" published in the Asian Power Electronics Journal, Vol.5 No.1, Aug 2011, in which a fixed blocking voltage for each semiconductor may be set. However due to a complex configuration of components and therefore hard to implement with respect to high frequency (HF) properties as well as an inevitable large amount of stray inductance due to a series connection of several semiconductors in combination with the additional deficiencies as described above, the prior art concept will have limitations in order to achieve a well-designed switching power converter setting.

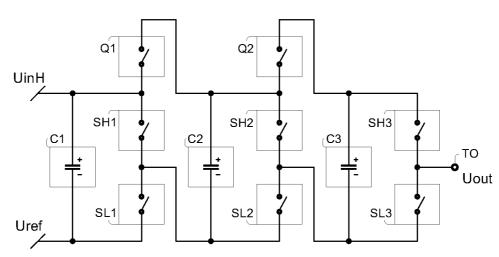

A switching charge pump setting of the prior art as shown in Figure 1 implemented with a plurality of switching elements and capacitive elements may generate a summated positive switching output voltage Uout provided at terminal TO with respect to a reference voltage Uref, in which each of the respective capacitive elements C1, C2 and C3 may be charged during operation to a voltage level equal to a voltage between a supply voltage UinH and the reference voltage Uref to generate a peak-peak value of the summated positive switching output voltage Uout with respect to the reference voltage equal to a summation of each voltage level provided across the respective capacitive elements C1, C2 and C3. In operation the switching charge pump setting as shown in Figure 1 may employ in response to a control signal two operational states during a switching period being associated with an operational switching frequency of the switching charge pump setting. During a first operational state the switching charge pump setting may provide a switched voltage Uout equal to the reference voltage Uref, in which the switching elements SL1, SL2, SL3, Q1 and Q2 are conductive in combination with the switching elements SH1, SH2 and SH3 being non-conductive, and in which the capacitive elements C2 and C3 may be charged to a voltage level equal to a voltage between the supply voltage UinH and the reference voltage Uref. During a second operational state the switching charge pump setting may provide a summated positive switched output voltage Uout with respect to the reference voltage Uref equal to the summation of each voltage provided across the respective capacitive elements C1, C2 and C3, in which the switching elements SH1, SH2 and SH3 are conductive in combination with switching elements SL1, SL2, SL3, Q1 and Q2 being non-conductive. The switching charge pump setting as shown in the Figure 1 exhibits a non-balanced configuration generating a non-balanced switching output voltage Uout with respect to the reference voltage Uref and therefore additional means may be implemented such as for example a DC bias voltage

10

15

20

25

30

35

or a DC blocking capacitor to provide a balanced switching output voltage with respect to a reference voltage, in which the additional means may affect the signal characteristics of the balanced switching output voltage negatively.

The switching charge pump setting of the prior art as shown in Figure 1 may be implemented in an opposite variant thereof as well (not shown) for generating a summated negative switching output voltage with respect to a reference voltage as will be well understood by those skilled in the art.

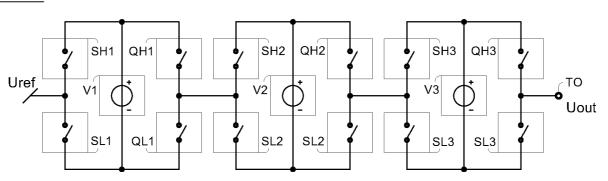

A combination of the switching charge pump setting as shown in Figure 1 and the opposite variant thereof may result in a switching charge pump setting as shown in Figure 2 for generating a summated positive as well as negative switching output voltage Uout provided at terminal TO with respect to a reference voltage Uref, in which each of the respective capacitive elements C1, C2, C3 and C4 may be charged during operation to a voltage level equal to a voltage between a supply voltage UinH and the reference voltage Uref to generate a peak-peak value of the summated positive and negative switching output voltage Uout equal to a summation of each voltage level provided across the respective capacitive elements C1, C2, C3 and C4. In operation the switching charge pump setting as shown in Figure 2 may employ in response to a control signal two operational states during a switching period being associated with an operational switching frequency of the switching charge pump setting. During a first operational state the switching charge pump setting may provide a summated positive switched output voltage Uout with respect to the reference voltage Uref equal to the summation of each voltage provided across the capacitive elements C1 and C3, in which the switching elements SH1, SH2, SH3, SH4, Q1 and Q3 are conductive in combination with the switching elements SL1, SL2, SL3, SL4 and Q2 being non-conductive, and in which capacitive element C2 may be charged to a voltage level equal to a voltage across capacitive element C1 and capacitive element C4 may be charged to a voltage level equal to a voltage across capacitive element C3. During a second operational state the switching charge pump setting may provide a summated negative switched output voltage Uout with respect to the reference voltage Uref equal to the summation of each voltage provided across the capacitive elements C2 and C4, in which the switching elements SL1, SL2, SL3, SL4 and Q2 are conductive in combination with switching elements SH1, SH2, SH3, SH4, Q1 and Q3 being non-conductive, and in which capacitive element C3 may be charged to a voltage level equal to a voltage across capacitive element C2. Consequently the switching charge pump setting as shown in Figure 2 may generate the summated positive as well as negative switching output voltage Uout with respect to the reference voltage Uref, in which the use of additional DC bias means as well as DC blocking capacitor means may be

10

15

20

25

30

35

4

omitted. However it is to be noted that the switching charge pump setting as shown in Figure 1 as well as the opposite variant thereof exhibits a non-balanced circuit configuration resulting in case the respective switching elements are implemented with for example semiconductors (MOSFET, IGBT, BJT, DIODE) in a varying output capacitance being non-balanced along a rising edge transition with respect to the varying output capacitance along a falling edge transition of a summated switching output voltage and therefore resulting in a deviation between a rising edge transition time and a falling edge transition time of the summated switching output voltage. Consequently the deviation in transition times will affect performance negatively in a time related setting employing for example a summated switching output voltage being pulse width modulated (PWM). Subsequently the combination of the switching charge pump setting as shown in Figure 1 and the opposite variant thereof aiming at a balanced circuit configuration of a switching charge pump setting as shown in Figure 2 and therefore aiming at a balanced output capacitance will result in a generation of a summated positive as well as negative switching output voltage Uout with respect to a reference voltage Uref comprising residual non-balanced signal properties in a time related as well as a voltage related domain and consequently reduced performance. As described above US3748492 discloses such prior art switching charge pump settings in accordance with both the Figures 1 and 2.

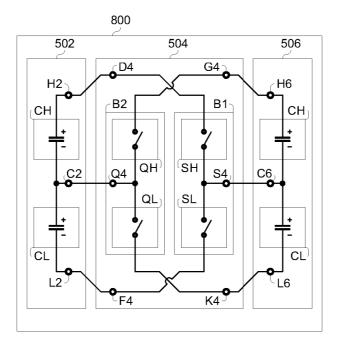

A switching power converter as shown in Figure 3 comprises a plurality of full bridge power stages connected in cascade, in which the switching power converter may generate a summated positive as well as negative switching output voltage Uout provided at terminal TO with respect to a reference voltage Uref equal to a summation of each voltage provided across the respective voltage sources V1, V2 and V3. The switching power converter as shown in Figure 3 exhibits a balanced circuit configuration, in which the balanced circuit configuration may result in case the respective switching elements are implemented with for example semiconductors (MOSFET, IGBT, BJT) in a varying output capacitance being balanced along a rising edge transition with respect to the varying output capacitance along a falling edge transition of the summated positive as well as negative switching output voltage Uout and therefore may result in a rising edge transition time being identical to a falling edge transition time of the summated positive as well as switching output voltage. In operation the switching power converter as shown in Figure 3 may employ in response to a control signal two operational states during a switching period being associated with an operational switching frequency of the switching power converter. During a first operational state the switching power converter may provide a summated positive switched output voltage Uout with respect to the reference voltage Uref equal to the summation of each voltage provided across the respective

10

15

20

25

30

voltage sources V1, V2 and V3, in which the switching elements SL1, QH1, SL2, QH2, SL3 and QH3 are conductive in combination with the switching elements SH1, QL1, SH2, SL2, SH3 and SL3 being non-conductive. During a second operational state the switching power converter may provide a summated negative switched output voltage Uout with respect to the reference voltage Uref equal to the summation of each voltage provided across the respective voltage sources V1, V2 and V3, in which the switching elements SH1, QL1, SH2, SL2, SH3 and SL3 are conductive in combination with switching elements SL1, QH1, SL2, QH2, SL3 and QH3 being nonconductive. US6160445 discloses such a prior art switching power converter. In contrast to the switching charge pump settings as shown in the Figures 1 and 2 the switching power converter generally requires an independent voltage source V1,V2 and V3 for each full bridge switching power stage as shown in Figure 3 being galvanically isolated with respect to the reference voltage Uref to operate properly due to a lack of a charge pump capability as described in accordance with the Figures 1 and 2. Subsequently the implementation of a voltage source being galvanically isolated with respect to the reference voltage Uref may yield a capacitive coupling between an isolated barrier (not shown) of the voltage source being galvanically isolated and a reference node (not shown) providing the reference voltage Uref, in which an implementation of a transformer (not shown) comprising a parasitic interwinding capacitance and therefore the capacitive coupling between a first and second winding for providing the isolated barrier is commonly used. Consequently due to a capacitance of each capacitive coupling between the respective voltage sources and the reference node accumulated forming an accumulated capacitive load the performance of the switching power converter may be severely degraded particularly in a high voltage setting employing a high operational switching frequency and aiming at fast transition times during switching, in which the accumulated capacitive load of the switching power converter may result in a high increase of switching losses and electromagnetic interference (EMI) during operation.

WO2012/151466A2 discloses an electric power convertor having a regulating circuit and a switching network. The regulating circuit maintains an average DC current through a magnetic storage element. The switching network includes charge storage elements connected to switches that are controllable to switch between plural switch configurations. Described is a step-down converter wherein the switching network is adiabatically charged using the regulating circuit.

10

15

20

25

30

35

**DESCRIPTION (06.03.2020)**

According to the above stated deficiencies that exist with prior art configurations, the objective of the present invention is to provide a switching power converter system capable of generating a high resolution well-balanced high voltage pulse-width-modulated (PWM) signal switched at a high operational switching frequency with fast balanced transition times in combination with a very energy efficient concept by means of a charge pump setting having a H8H topology.

The present invention provides a charge pump setting for use in a switching power converter according to claim 1. Further embodiments are defined in the dependent claims. Aspects and parts of the subject-matter of the description not covered by the claims constitute background art or examples useful for understanding the invention.

In accordance with the present invention the switching power converter system includes a charge pump component responsive to at least one pulse modulated control signal, in which the charge pump component comprises a crosswise switching charge pump setting implemented with at least two auxiliary units and at least one interlace unit. The crosswise switching charge pump setting comprises a configuration of an interlace unit intermediately coupled in cascade with an auxiliary unit being pre-coupled and an auxiliary unit being post-coupled to form a H8H topology, in which the interlace unit is one of the at least one interlace unit, and in which the auxiliary unit being pre-coupled and the auxiliary unit being post-coupled are two of the at least two auxiliary units. The interlace unit of the H8H topology is operable to couple in response to one or more of the at least one pulse modulated control signal the auxiliary unit being precoupled with the auxiliary unit being post-coupled repetitively in accordance with a high operational state and a low operational state of the interlace unit. The switching power converter system is characterised in that each of the at least two auxiliary units comprises a high side capacitance section and a low side capacitance section coupled in series as well as a high side terminal, a common side terminal and a low side terminal, in which the high side capacitance section is coupled between the high side terminal and the common side terminal, and in which the low side capacitance section is coupled between the common side terminal and the low side terminal. The interlace unit of the H8H topology is operable to couple during the high operational state the high side terminal of the auxiliary unit being pre-coupled with the common side terminal of the auxiliary unit being post-coupled and the common side terminal of the auxiliary unit being pre-coupled with the low side terminal of the auxiliary unit being postcoupled, and the interlace unit is operable to couple during the low operational state the common side terminal of the auxiliary unit being pre-coupled with the high side terminal of the auxiliary unit being post-coupled and the low side terminal of the auxiliary unit being pre-coupled with the common side terminal of the auxiliary unit being post-coupled.

10

15

20

25

30

35

7

In accordance with the present invention a crosswise switching charge pump setting implemented with at least two auxiliary units and at least one interlace unit may be configured to form one or more H8H topologies, in which an interlace unit being one of the at least one interlace unit is alternately coupled in cascade with an auxiliary unit being one of the at least two auxiliary units or a cluster comprising a parallel coupling of two or more of the at least two auxiliary units. In addition the crosswise switching charge pump setting may be started as well as ended with an auxiliary unit being one of the at least two auxiliary units, a cluster comprising the parallel coupling of two or more of the at least two auxiliary units or an interlink unit.

In accordance with the present invention a crosswise switching charge pump setting is implemented with at least two auxiliary units and at least one interlace unit, in which in particular a common side terminal of each of the at least two auxiliary units may be capable to provide a reference voltage, to provide the means for a coupling with for example a load, to provide the means for a coupling of the switching power converter system or a combination thereof, and in which an interlace unit being one of the at least one interlace unit includes an interlink terminal in particular capable to provide a positive switched voltage as well as negative switched voltage with respect to a reference voltage, to provide the means for a coupling with for example a load, to provide the means for a coupling of the switching power converter system or a combination thereof. In addition in accordance with the present invention the crosswise switching charge pump setting may comprise an interlink unit, in which the interlink unit may include an interlink terminal in particular capable to provide a positive as well as negative switched voltage with respect to a reference voltage, to provide the means for a coupling with for example a load, to provide the means for a coupling of the switching power converter system or a combination thereof.

In accordance with a further aspect of the present invention a crosswise switching charge pump setting implemented with at least two auxiliary units and at least one interlace unit may comprise the parallel coupling of two or more of the at least two auxiliary units to form a cluster, in which the cluster comprising the parallel coupling of two or more of the at least two auxiliary units may further comprise low pass filter means, resonant filter means, voltage regulator means, protection means, inrush current limiter means, current monitoring means or a combination thereof.

According to the further aspect of the present invention a cluster comprising the parallel coupling of two or more of the at least two auxiliary units may further comprise low pass filter means subdivided in high side low pass filter means and low side low pass filter means, in which two auxiliary units included in the parallel coupling of the cluster may comprise a coupling

10

15

20

25

30

35

between the high side terminals interposed by the high side low pass filter means, a coupling of the common side terminals and a coupling between the low side terminals interposed by the low side low pass filter means to set an attenuated frequency range between the high side terminals being interposed as well as to set an attenuated frequency range between the low side terminals being interposed. Subsequently a crosswise switching charge pump setting implemented with at least two auxiliary units and at least one interlace unit is configured to form a H8H topology of an interlace unit intermediately coupled in cascade with an auxiliary unit being pre-coupled and an auxiliary unit being post-coupled, in which the auxiliary unit being pre-coupled in cascade with the interlace unit is included in a parallel coupling of two or more of the at least two auxiliary units to form a cluster being pre-coupled to the interlace unit, and in which the auxiliary unit being post-coupled in cascade with the interlace unit is included in a parallel coupling of two or more of the at least two auxiliary units to form a cluster being post-coupled to the interlace unit. Consequently in case the cluster being pre-coupled as well as the cluster being post-coupled further includes high side low pass filter means and low side low pass filter means in a manner as described above, than the configuration of the H8H topology supplemented with snubber means may result in highly improved characteristic switching properties in a high frequency (HF) range of the interlace unit providing fast well-balanced transition times during switching, an absence of any ringing, and reduced electromagnetic interference (EMI). In addition the cluster being pre-coupled as well as the cluster being post-coupled further including high side low pass filter means and low side low pass filter means in a manner as described above may provide the means for increasing a physical distance between two of the at least one interlace unit as well as between one of the at least one interlace unit and an interlink unit without compromising the characteristic switching properties, in which an increase of the physical distance may provide the means for passive cooling as well as for an extended capacitance of one or more of the at least two auxiliary units.

In addition according to the further aspect of the present invention a cluster comprising a parallel coupling of two or more of the at least two auxiliary units may further comprise voltage regulator means interposed in a parallel coupling between two auxiliary units of the cluster, in which the voltage regulator means may comprise a linear regulator setting, a switched-mode power supply (SMPS) setting or a combination thereof operable to regulate, to restore, to adapt or a combination thereof for setting an adjusted voltage at an output of the voltage regulator means.

In accordance with the present invention a crosswise switching charge pump setting configured to form a H8H topology comprising a first circuit setting of an interlace unit being

10

15

20

25

30

35

preferred as will be described in detail hereinafter allows for a downright stable and a highly HF optimized concept capable of generating a high voltage pulse modulated signal in a kilovolt range, an output capacitor less (OCL) setting, a high operational switching frequency up to and above 5MHz, fast well-balanced transition times, a very energy efficient concept, four quadrant operation characteristic for driving a complex load, a single-bit setting for generating a two level summated positive switched voltage as well as negative switched voltage, a multi-bit setting for generating a multi-level positive switched voltage as well as a multi-level negative switched voltage, in which the multi-bit setting providing gradient capabilities may include a level of zero volt. Needless to say, that although the crosswise switching charge pump setting is in particular suitable for high voltage operation, low voltage operation in general may be suitable to a same extent.

It is to be noted, that the switching power converter system in the scope of the present invention is capable of operating at various voltage levels in conjunction with various power levels, with various pulse modulator topology settings, with various pulse modulation techniques, at various performance levels, in which the switching power converter system may employ one or more crosswise switching charge pump settings implemented in a single configuration, a differential configuration, a three-phase configuration or a poly-phase configuration.

Applications for the switching power converter system are numerous and may include Class-D amplification, Class-G amplification or a combination thereof to provide Class-H amplification, High Voltage power DAC for a direct drive of a capacitive load of an electrostatic loudspeaker, an electric motor, a magnetic resonance imaging system (MRI), an electron microscope, scientific applications in general, grid-tied inverter, generator-tied inverter, AC/AC converter, DC/AC converter, AC/DC converter and DC/DC converter.

### Short description of drawings

The present invention will be discussed in detail hereinafter exhibiting several exemplary embodiments with reference to the attached drawings that are intended to illustrate the present invention but not to limit its scope which is defined by the annexed claims and its equivalent embodiment, in which

Figure 1 illustrates a schematic diagram showing a switching charge pump setting of the prior art capable of generating a summated positive switching output voltage,

10

15

20

25

30

35

Figure 2 illustrates a schematic diagram showing a switching charge pump setting of the prior art capable of generating a summated positive as well as negative switching output voltage,

Figure 3 illustrates a schematic diagram showing a switching power converter of the prior art capable of generating a summated positive as well as negative switching output voltage,

Figure 4 illustrates a basic conceptual block diagram of a switching power converter system,

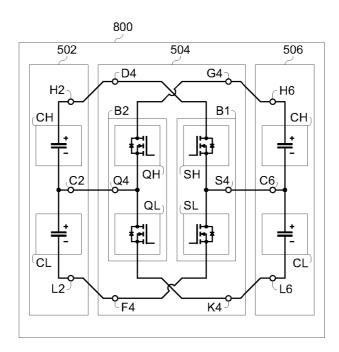

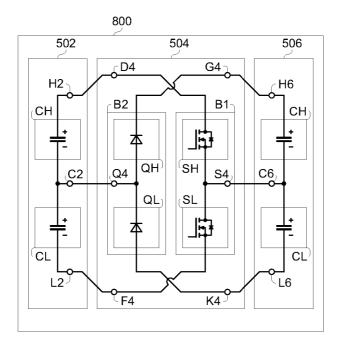

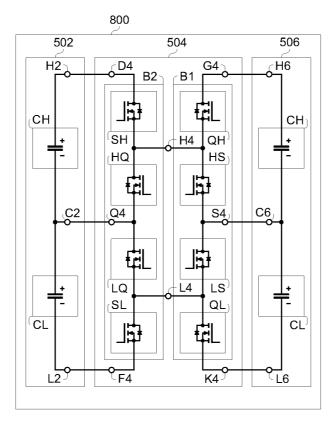

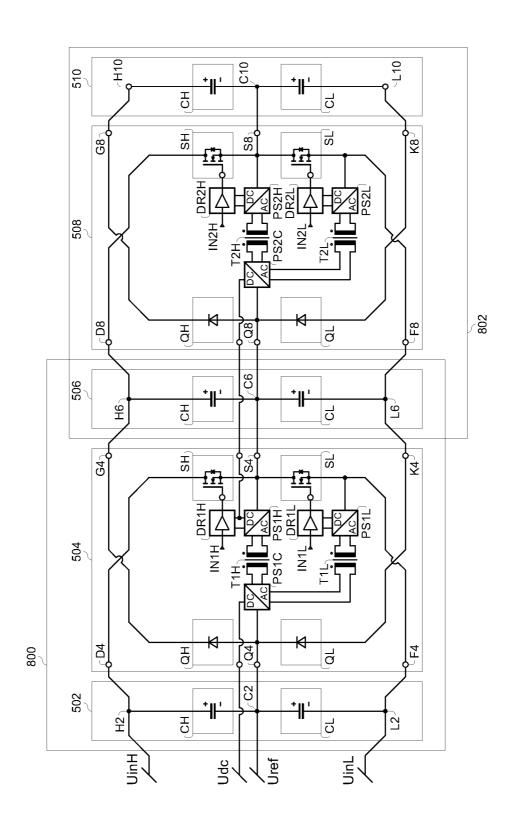

Figure 5 illustrates a configuration of a H8H topology comprising a first circuit setting of an interlace unit being preferred,

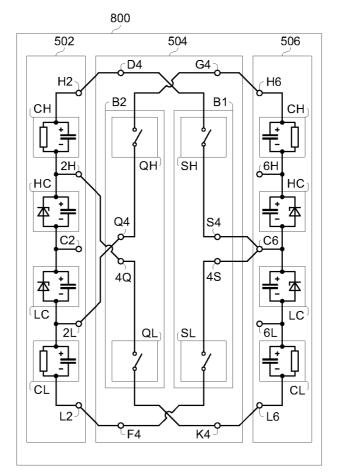

Figure 5A illustrates the configuration of the H8H topology comprising the first circuit setting being the preferred constituted with actively driven semiconductors,

Figure 5B illustrates the configuration of the H8H topology comprising the first circuit setting being the preferred constituted with passively and actively driven semiconductors,

Figure 5C illustrates the configuration of the H8H topology comprising a variation of the circuit diagram as shown in Figure 5 for adjusting means,

Figure 5D illustrates the configuration of the H8H topology comprising a variation of the circuit diagram as shown in Figure 5 for adjusting means,

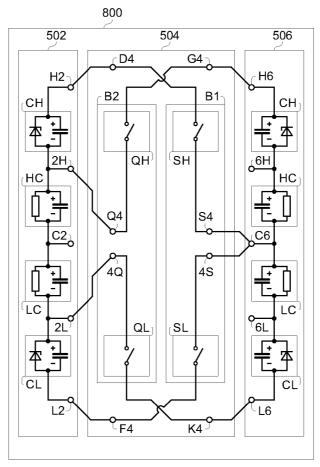

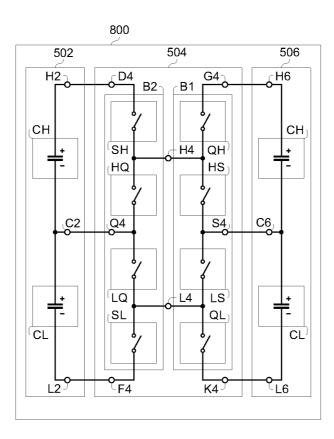

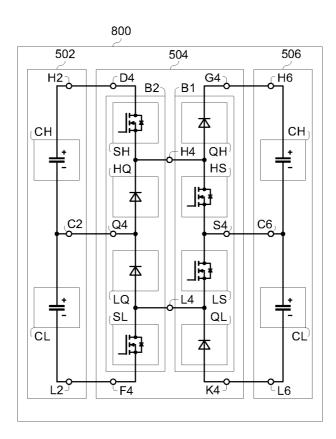

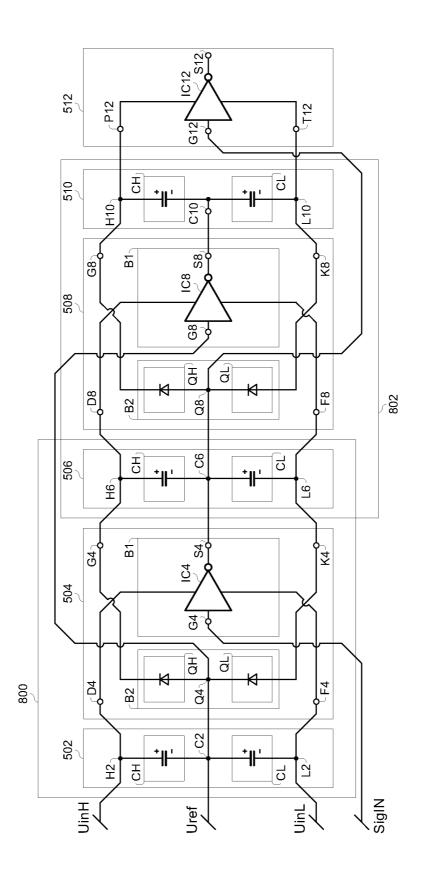

Figure 6 illustrates the configuration of the H8H topology comprising a second circuit setting of the interlace unit being an alternative,

Figure 6A illustrates the configuration of the H8H topology comprising the second circuit setting being the alternative constituted with actively driven semiconductors,

Figure 6B illustrates the configuration of the H8H topology comprising the second circuit setting being the alternative constituted with passively and actively driven semiconductors,

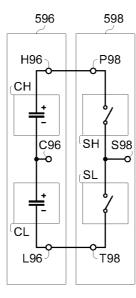

Figure 7 illustrates a circuit diagram an interlink unit coupled in cascade with an auxiliary unit being pre-coupled,

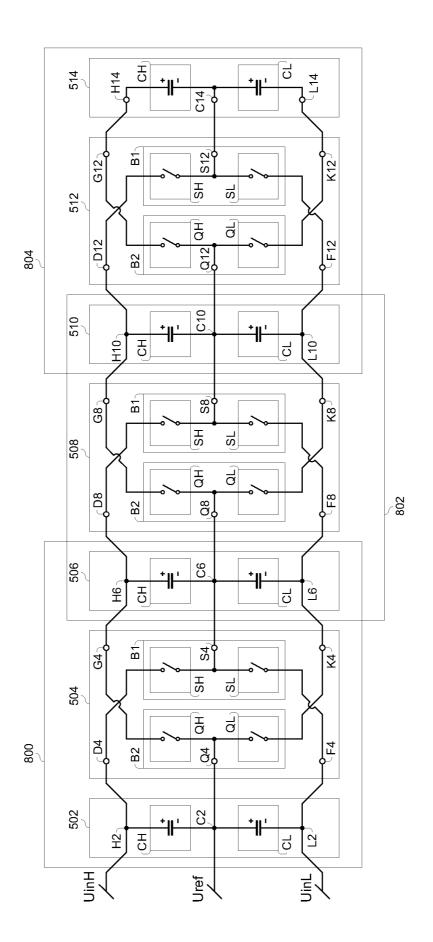

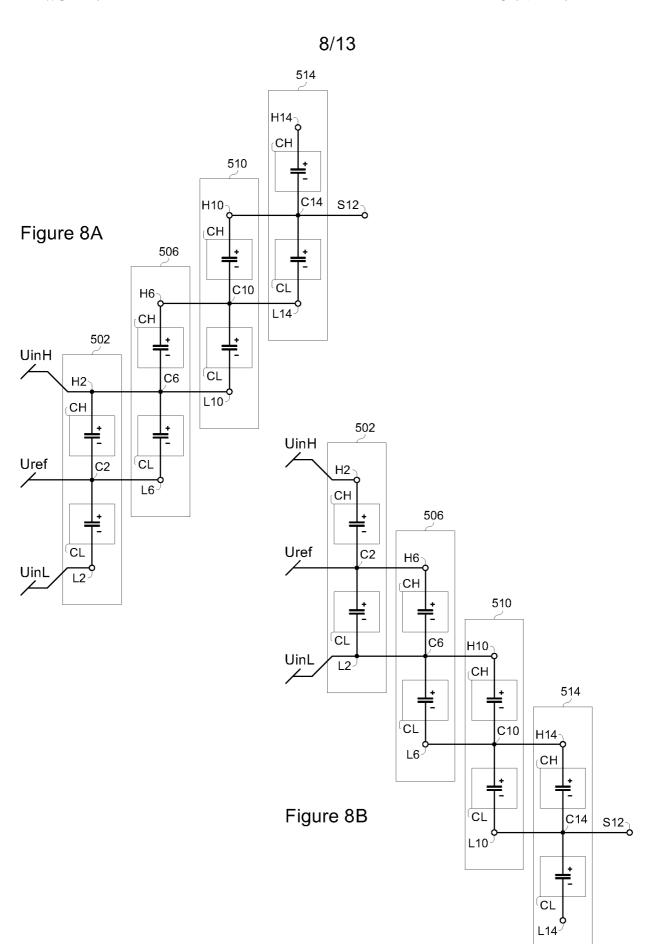

Figure 8 illustrates a circuit diagram of a crosswise switching charge pump setting configured with three H8H topologies overlapping one another,

Figure 8A illustrates in accordance with the circuit diagram as shown in Figure 8 the manner of the high side and the low side capacitance sections being coupled during the high operational state of each of the interlace units,

Figure 8B illustrates in accordance with the circuit diagram as shown in Figure 8 the manner of the high side and the low side capacitance sections being coupled during the low operational state of each of the interlace units,

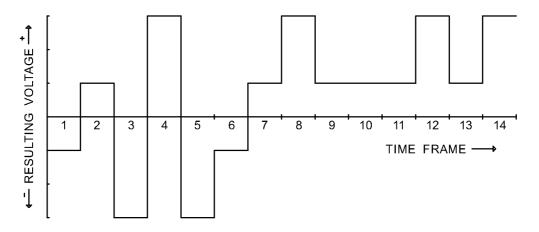

Figure 9 illustrates a resulting voltage generated arbitrarily during a time frame being one of fourteen time frames,

10

15

20

25

30

35

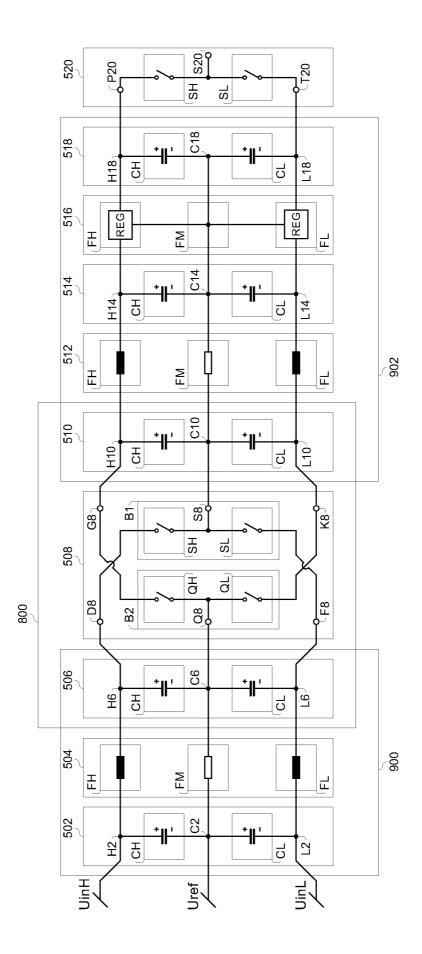

Figure 10 illustrates a circuit diagram of a crosswise switching charge pump setting implemented with configuration of a H8H topology, an interlink unit an two clusters in accordance with a further aspect of the present invention,

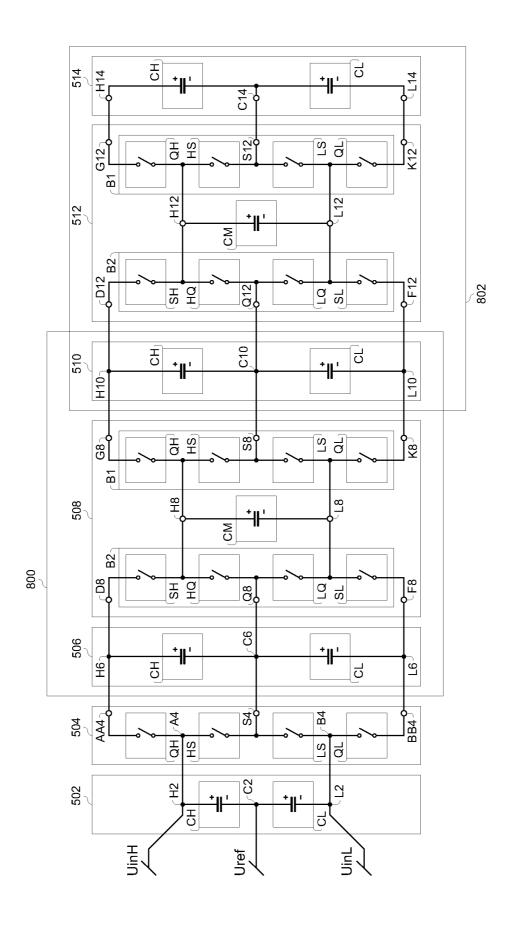

Figure 11 illustrates a circuit diagram of an extended auxiliary unit and an extended switching unit coupled in cascade with a crosswise switching charge pump setting configured with two H8H topologies overlapping one another,

Figure 12 illustrates a circuit diagram of a crosswise switching charge pump setting supplemented with galvanic isolated power supply means as well as gate drive means,

Figure 13 illustrates a circuit diagram of a crosswise switching charge pump setting constituted in part with integrated circuits and characterised as a ripple through converter asynchronously controlled.

#### **Description of exemplary embodiments**

In accordance with the present invention a basic conceptual block diagram of a switching power converter system as shown in Figure 4 may comprise a receiving component BLOCK 1, a control component BLOCK 2, a link component BLOCK 3, a power source component BLOCK 4 and a charge pump component BLOCK 5, in which the basic conceptual block diagram of the switching power converter system is supplemented with a load component BLOCK 6.

As illustrated in Figure 4 BLOCK 1 a receiving component may comprise signal input means at an input of the switching power converter system, in which the signal input means may be configured to receive one or more input signals such as for example an analogue formatted input signal, a digital formatted input signal, a pulse modulated input signal in general, a pulse modulated control signal being one of at least one pulse modulated control signal generated for the charge pump component as shown in Figure 4 BLOCK 5, a pulse width modulated input signal, a feedback signal for adjusting characteristic signal properties of the switching power converter system in response to the feedback signal, a feed forward signal for adjusting characteristic signal properties of the switching power converter system in response to the feed forward signal, a clock signal for synchronisation means, a carrier frequency for pulse modulation means or a combination thereof. Needless to say that an implementation of the signal input means may be balanced, unbalanced, optical, wireless or a combination thereof.

As illustrated in Figure 4 BLOCK 2, a control component may be configured to generate at least one pulse modulated control signal for the charge pump component as shown in Figure 4 BLOCK 5, in which a pulse modulated control signal being one of the at least one pulse

10

15

20

25

30

35

modulated control signal may comprise a pulse width modulated signal (PWM), a pulse density modulated signal (PDM) or a combination thereof. A pulse modulated control signal being one of the at least one pulse modulated control signal may be configured to control for example an actively driven semiconductor or an integrated switching power module included in a crosswise switching charge pump setting part of the charge pump component as shown in Figure 4 BLOCK 5. A pulse modulated control signal being one of the at least one pulse modulated control signal may be generated in response to the one or more input signals of the signal input means part of the receiving component as shown in Figure 4 BLOCK 1, in response to internal circuitry of the control component or a combination thereof, in which for example a pulse modulated control signal being one of the at least one pulse modulated control signal is responsive to the internal circuitry of the control component in order to maintain proper operation of a crosswise switching charge pump setting part of the charge pump component and more specific to maintain a charged status of at least two auxiliary units included in the crosswise switching charge pump setting during an absence of the one or more input signals of the signal input means. It is to be emphasised that a pulse modulated control signal being one of the at least one pulse modulated control signal may be emanated from the receiving component as shown in Figure 4 BLOCK 1, a pulse modulated control signal being one of the at least one pulse modulated control signal may be emanated from the control component as shown in Figure 4 BLOCK 2 or a combination thereof, in which the control component may be omitted in whole or in part.

In accordance with protection means and supporting means the control component may comprise for example a limiter function obviating possible over-modulation of a pulse modulated control signal being one of the at least one pulse modulated control signal, in which the limiter function may maintain a minimum and a maximum duty cycle of the pulse modulated control signal in order to be limited within a minimum pulse width as being set, and according to signal support means the control component may comprise a delay timing control, in which the delay timing control is configured to adapt the pulse modulated control signal by adding a delay time also called dead time to delay a rising edge transition or a falling edge transition of the pulse modulated control signal resulting in a delay of a transition from a non-conductive state into a conductive state of for example an actively driven semiconductor being responsive to the pulse modulated control signal. The delay timing control is commonly used to prevent cross conduction during a voltage transition of for example two counter phase and actively driven semiconductors series connected in a half bridge setting as will be well understood by those skilled in the art.

10

15

20

25

30

35

In accordance with pulse modulator means the control component may comprise a pulse modulation setting being well-known or more application specific employing for example pulse width modulation, pulse density modulation or a combination thereof, in which the pulse modulator setting may be analogue based, digital based or a combination thereof such as for example a self-oscillating pulse modulator, a delta-sigma modulator, field-programmable gate array (FPGA) in conjunction with a pulse modulator embedded in software or an audio related TAS5558 HD PWM processor from Texas Instruments supplemented with a sample rate converter (SRC) and a digital signal processor (DSP).

In addition according to the pulse modulator setting the control component may be configured to generate the at least one pulse modulated control signal by means of for example the pulse modulator setting being single-bit configured in an AD modulation mode for driving a crosswise switching charge pump setting part of the charge pump component as shown in Figure 4 BLOCK 5, a pulse width modulator setting being dual-bit configured in a BD modulation mode for driving two crosswise switching charge pump settings differentially implemented or a pulse modulator setting being multi-bit configured for driving one or more crosswise switching charge pump settings to provide gradient capabilities, in which two or more of the at least one pulse modulated control signal independently of one another may be generated with different switching periods in a time domain as well as in a frequency domain by means of the pulse modulator setting being multi-bit configured.

A link component as shown in Figure 4 BLOCK 3 may comprise a transmission link for conducting a pulse modulated control signal being one of the at least one pulse modulated control signal exhibiting a key part with respect to the characteristic switching properties of a crosswise switching charge pump setting part of the charge pump component as shown in Figure 4 BLOCK 5. Subsequently for a proper operation of the crosswise switching charge pump setting it may be vital to implement the transmission link comprising a galvanically isolated barrier to obtain floating properties of for example an actively driven semiconductor being responsive to the pulse modulated control signal and being one of the respective actively driven semiconductors included in the crosswise switching charge pump setting, in which each of the respective actively driven semiconductors may be responsive to a pulse modulated control signal being conducted by means of using a transmission link comprising a galvanically isolated barrier to obtain the proper operation. In addition a transmission link comprising a galvanically isolated barrier, in which another part of the transmission link comprising the galvanically isolated barrier may be constituted with an electrical signal conductor coupled to the

10

15

20

25

30

35

optical signal conductor. The electrical signal conductor may be implemented with for example an embedded track on a printed circuit board (PCB), a coaxial conductor or a shielded twisted pair conductor and the like, in which the electrical signal conductor may comprise a characteristic impedance as constant as possible along a physical path length of the electrical signal conductor, and in which a resistive element may be coupled to an input of the electrical signal conductor equal to the characteristic impedance without the use of any termination means coupled to an output of the electrical signal conductor other than for example a capacitive input impedance at an input of a fast switching current source coupled to the output.

It is to be noted, that an implementation of a transmission link comprising a galvanically isolated barrier is not limited to an optical signal conductor to obtain the galvanically isolated barrier by means of an optically coupled signal conductor and may include transformer means to obtain a galvanically isolated barrier by means of a magnetically coupled signal conductor.

An objective of a transmission link is to maintain integrity of the characteristic signal properties of a pulse modulated control signal being one of the at least one pulse modulated control signal.

A first arrangement according to the objective of the transmission link relates to the pulse modulated control signal converted into two triggering pulse signals comprising trigger pulses, in which a trigger pulse being one of the trigger pulses may exhibit a maximum pulse duration of two times a minimum pulse duration of the pulse modulated control signal. For example a trigger pulse of a first triggering pulse signal is derived from each rising edge transition of the pulse modulated control signal and a trigger pulse of a second triggering pulse signal is derived from each falling edge transition of the pulse modulated control signal, in which a switching frequency of the first triggering pulse signal as well as the second triggering pulse signal will be halved with respect to an operational switching frequency of the pulse modulated control signal. In a case the pulse modulated control signal is pulse width modulated the first arrangement may result in a low frequency signal in the range of for example 20Hz to 70KHz such as an audio formatted signal being mainly encompassed in a phase related condition between the first triggering pulse signal and second triggering pulse signal rather than a time related condition in accordance with the pulse modulated control signal, in which the first triggering pulse signal as well as the second triggering pulse signal exhibit nearly constant characteristic signal properties in a high frequency range starting at for example 100KHz providing a nearly constant amplitude correlation between the harmonics. It is to be noted that a pulse modulated control signal may be converted in one triggering pulse signal as well, the one triggering pulse signal comprising trigger pulses, in which a trigger pulse being one of the trigger pulses may exhibit a maximum

10

15

20

25

30

35

pulse duration equal to a minimum pulse duration of the pulse modulated control signal. For example a trigger pulse of the one triggering pulse signal may be derived from each rising edge transition of the pulse modulated control signal and a trigger pulse of the one triggering pulse signal may be derived from each falling edge transition of the pulse modulated control signal, in which a trigger pulse derived from each rising edge transition exhibits a pulse duration twice as long as a trigger pulse derived from each falling edge transition for distinguishing a rising edge transition from a falling edge transition to maintain the correct signal level information in case the one triggering pulse signal is converted back into the pulse modulated control signal. Alternatively rather than a trigger pulse exhibiting the pulse duration twice as long two or more trigger pulses may be generated in response to a rising edge transition of the pulse modulated control signal for distinguishing a trigger pulse being single in response to a falling edge transition of the pulse modulated control signal provided that a maximum duration of two or more trigger pulses may be equal to the minimum pulse duration of the pulse modulated control signal.

A second arrangement according to the objective of the transmission link relates to a transmission link comprising a galvanic isolated barrier as described above, in which the transmission link comprising the galvanic isolated barrier may be implemented with two signal conductors. In accordance with the first arrangement a first signal conductor may conduct a first triggering pulse signal and a second signal conductor may conduct a second triggering pulse signal, in which the first triggering pulse signal and the second triggering pulse signal are derived from a pulse modulated control signal being one of the at least one pulse modulated control signal. In addition the first signal conductor as well as the second signal conductor may be constituted with an electrical signal conductor coupled to an optical signal conductor, in which the first signal conductor and the second signal conductor may be substantially identical to obtain an equal delay time for the first triggering pulse signal and the second triggering pulse signal during conduction.

On a basis of the first signal conductor being substantially identical to the second signal conductor an implementation of the optical signal conductor of the first signal conductor will be described hereinafter, in which the implementation of the optical signal conductor of the second signal conductor will be described accordingly. Subsequently the optical signal conductor of the first signal conductor may be implemented with an optical transmitter as well as an optical receiver, in which an output of the optical transmitter coupled to an input of the optical signal conductor may be constituted with an infra-red light emitting diode (IR LED) comprising a high radiant intensity rating and fast switching times. In addition an input of the optical transmitter

10

15

20

25

30

35

may be coupled to an output of a fast switching current source and the input of the fast switching current source may be coupled to the output of the electrical signal conductor, in which during a conducting state the infra-red light emitting diode may be driven with a current pulse generated by the fast switching current source in response to the first triggering pulse signal for converting the first triggering pulse signal having electrical properties into the first triggering pulse signal having optical properties, in which a time duration of the conducting state may be equal to a time duration of a trigger pulse as being set for the first triggering pulse signal.

An optical receiver having an input coupled to an output of the optical signal conductor may be constituted with a photodiode comprising a fast response time such as for example a silicon PIN photodiode for converting the first triggering pulse signal having optical properties presented at the input of the optical receiver back into the first triggering pulse signal having electrical properties provided at an output of the optical receiver, in which the photodiode may employ a photoconductive mode (PC) in conjunction with a relative high reverse voltage resulting during the conducting state in response of the first triggering pulse signal in a current through the photodiode being in a near saturated or saturated condition, and in which the output of the optical receiver may provide the output of the first signal conductor.

A third arrangement according to the objective of the transmission link relates to the implementation of the optical signal conductor of the first signal conductor as will be described hereinafter, in which the implementation of the optical signal conductor of the second signal conductor will be described accordingly. Subsequently the optical signal conductor of the first signal conductor having the input coupled to the output of the optical transmitter and the output of the optical signal conductor coupled to the input of the optical receiver, in which the optical signal conductor exhibits a light guide implemented with a straight hollow tube comprising a cylindrical outer surface and a cylindrical inner surface such as for example a straight hollow tube made of glass or acrylic comprising the cylindrical inner surface being as smooth and reflective as possible. In addition the straight hollow tube may comprise an inner cross section at an input aperture representing the input of the optical signal conductor, in which the input aperture is sufficiently large to capture a pulsating radiant flux signal provided at the output of the optical transmitter in response to the first triggering pulse signal. The optical transmitter providing the pulsating radiant flux signal may transmit during the conducting state an emission of rays, in which the emission of rays may enter at a centre of the input aperture on a longitudinal axis of the straight hollow tube. In addition the optical transmitter may comprise a sufficiently narrow emission angle to reflect all rays being struck on the cylindrical inner surface of the straight hollow tube from the input aperture up to an output aperture, in which the

10

15

20

25

30

35

cylindrical outer surface to the cylindrical inner surface of the straight hollow tube may be substantially transparent, and the reflected rays in conjunction with non-reflected rays at angles near as well as on the longitudinal axis defined as a density of rays, in which the density of rays may provide a pulsating radiant flux signal comprising a near uniform high radiant intensity at the output aperture of the straight hollow tube representing the output of the optical signal conductor. According to the optical receiver the input may exhibit a circular optical input comprising a cross section being sufficiently large to capture the pulsating radiant flux signal being provided at the output aperture of the straight hollow tube, in which the first triggering pulse signal having electrical properties may be provided at the output of the optical receiver in response to the pulsating radiant flux signal represented by the first triggering pulse signal having optical properties.

In accordance with the first and second arrangement the transmission link may be implemented with a bi-stable flip-flop circuit being operated by binary signals, in which the output of the first signal conductor may be coupled to a first input of the bi-stable flip-flop circuit for providing the first triggering pulse signal and an output of the second signal conductor may be coupled to a second input of the bi-stable flip-flop circuit for providing the second triggering pulse signal. Subsequently the bi-stable flip-flop circuit may be operable to combine the first triggering pulse signal and the second triggering pulse signal for converting back the pulse modulated control signal provided at an output of the bi-stable flip-flop circuit as will be well understood by those skilled in the art.

A power source component as shown in Figure 4 BLOCK 4 may comprise a dual voltage source coupled to a crosswise switching charge pump setting part of the charge pump component as shown in Figure 4 BLOCK 5, in which the dual voltage source may be constituted with a positive voltage terminal, a common voltage terminal and a negative voltage terminal. In addition a voltage provided between the positive voltage terminal and the common voltage terminal may be equal to a voltage provided between the common voltage terminal and the negative voltage terminal, in which the common voltage terminal may provide a reference voltage for the crosswise switching charge pump setting as well as for the switching power converter system.

The dual voltage source may be rated for sourcing power as well as sinking power at both the positive voltage terminal and the negative voltage terminal in conjunction with the common voltage terminal to handle for example complex power, in which a reactive power part of the complex power may dominate an active or real power part of the complex power being handled resulting in a periodic exchange of reactive power between the dual voltage source and the

10

15

20

25

30

35

crosswise switching charge pump setting, whereas the active power part being sourced by means of the dual voltage source may be derived from for example the AC mains, a battery supply, a voltage generator or a combination thereof.

From a point of view of the switching power converter system coupled to a load component Figure 4 BLOCK 6, the load component may comprise a load coupled to the crosswise switching charge pump setting. Subsequently the dual voltage source, the crosswise switching charge pump setting and the load may provide an interactive coherent embodiment for exchanging or transferring power, energy or electrical charge per unit of time, in which by means of interaction the load may be driven in accordance with the specifications as being set. For example the interactive coherent embodiment including the load being complex may handle the complex power characterised of a relationship between the active or real power part and the reactive power part. According to the switching power converter system coupled to the load of the load component Figure 4 BLOCK 6, the load component may be replaced by a voltage source coupled to the crosswise switching charge pump setting. Subsequently the dual voltage source, the crosswise switching charge pump setting and the voltage source may provide an interactive coherent embodiment for transferring electrical power, electrical energy or electrical charge per unit of time. For example the interactive coherent embodiment including the voltage source being a voltage generator may handle a transfer of electrical charge per unit of time from the voltage generator sourcing electrical energy towards the dual voltage source sinking the electrical energy. Subsequently the dual voltage source may transfer the electrical energy to for example the AC mains, a battery supply, a capacitor bank or a combination thereof.

In accordance with a supporting voltage provided between the positive voltage terminal and the negative voltage terminal of the dual voltage source, the supporting voltage may be set for example manually to a fixed voltage or in response to a galvanic isolated control signal emanated from a microprocessor, in which the supporting voltage may be adjusted over a predefined voltage range to adjust in a proportional degree a summated positive switched voltage as well as a summated negative switched voltage provided at an interlink terminal of the crosswise switching charge pump setting with respect to the reference voltage presented at the common voltage terminal.

According to the power source component comprising the dual voltage source, the dual voltage source may be implemented with a power supply topology being well-known in the art such as for example a linear power supply setting, a switched mode power supply setting (SMPS), a battery supply setting or a combination thereof, in which the power source component may be constituted with for example galvanic isolation means, low pass filter means, protection

10

15

20

25

30

35

means, connection means, as well as current limiting means, in which the current limiting means may provide a maximum current limit for the dual voltage source as well as for the interactive coherent embodiment including for example the load as described above.

It is to be noted that the power source component is not limited to an implementation of the dual voltage source as described above and may comprise for example instead of the dual voltage source a single voltage source constituted with an additional centre tap by means of a (active)virtual common voltage terminal.

Needless to say, that the switching power converter system may comprise for example two or more crosswise switching charge pump settings each constituted with a dual voltage source, a dual voltage source constituted with the two or more crosswise switching charge pump settings or a combination thereof, in which the power source component may include an accessory power supply for powering system components of the switching power converter system.

It is to be emphasised that the switching power converter system comprising a configuration of for example an AC to AC (alternating current) converter the power source component may be omitted in whole or in part as will be described hereinafter.

The following embodiments of the present invention encompassing various implementations of the crosswise switching charge pump setting comprising the configuration of the H8H topology will now be described more specifically.

It is to be emphasised that the following descriptions of the present invention with reference to the following embodiments of the various implementations of a crosswise switching charge pump setting are presented herein for purpose of illustration and description only, in which the precise forms disclosed are not intended to be exhaustive or to be limited. In addition the various implementations of a crosswise switching charge pump setting in accordance with the present invention resides not only in any of the following embodiments taken alone, but rather in the particular combination of all of its configurations as well as all of its interrelationships for the functions specified.

It is to be noted, that the term "connected" as being used in the following descriptions of the present invention and in the annexed claims means a direct electrical connection between two electrical elements without any electrical interrupts, whereas the term "coupled" means a direct electrical connection as well as an indirect electrical connection through one or more passive or active intermediary elements.

In accordance with the present invention the switching power converter system includes a charge pump component as illustrated in Figure 4 BLOCK 5 responsive to at least one pulse

10

15

20

25

30

35

modulated control signal emanated from the control component as shown in Figure 4 BLOCK 2, the receiving component as shown in Figure 4 BLOCK 1 or a combination thereof, in which the charge pump component comprises a crosswise switching charge pump setting implemented with at least two auxiliary units and at least one interlace unit. The crosswise switching charge pump setting may comprise a configuration as shown in Figure 5 as well as a configuration as shown in Figure 6 of an interlace unit 504 intermediately coupled in cascade with an auxiliary unit being pre-coupled 502 and an auxiliary unit being post-coupled 506 to form a H8H topology 800, in which the interlace unit 504 is one of the at least one interlace unit, and in which the auxiliary unit being pre-coupled 502 and the auxiliary unit being post-coupled 506 are two of the at least two auxiliary units. The interlace unit of the H8H topology 800 is operable to couple in response to one or more of the at least one pulse modulated control signal the auxiliary unit being pre-coupled with the auxiliary unit being post-coupled repetitively in accordance with a high operational state and a low operational state of the interlace unit. The switching power converter system is characterised in that each of the at least two auxiliary units comprises a high side capacitance section CH and a low side capacitance section CL coupled in series as well as a high side terminal, a common side terminal and a low side terminal, in which the high side capacitance section CH is coupled between the high side terminal and the common side terminal, and in which the low side capacitance section CL is coupled between the common side terminal and the low side terminal. The interlace unit of the H8H topology is operable to couple during the high operational state the high side terminal H2 of the auxiliary unit being pre-coupled with the common side terminal C6 of the auxiliary unit being post-coupled and the common side terminal C2 of the auxiliary unit being pre-coupled with the low side terminal L6 of the auxiliary unit being post-coupled, and the interlace unit is operable to couple during the low operational state the common side terminal C2 of the auxiliary unit being pre-coupled with the high side terminal H6 of the auxiliary unit being post-coupled and the low side terminal L2 of the auxiliary unit being pre-coupled with the common side terminal C6 of the auxiliary unit being postcoupled.

According to each of the at least two auxiliary units included in the crosswise switching charge pump setting the high side capacitance section CH comprises at least one capacitive element coupled between the high side terminal and the common side terminal, and the low side capacitance section CL comprises at least one capacitive element coupled between the common side terminal and the low side terminal. In addition a capacitive element being one of the at least one capacitive element of the high side capacitance section or being one of the at least one capacitive element of the low side capacitance section may be for example a capacitor, a polar

10

15

20

25

30

35

capacitor, a bipolar capacitor, an electrolytic capacitor, a ceramic capacitor, a polypropylene film capacitor, a SMT capacitor, a battery or a battery supply. Subsequently two or more capacitive elements being two or more of the at least one capacitive element of the high side capacitance section or being two or more of the at least one capacitive element of the low side capacitance section may be coupled in series, coupled in parallel or a combination thereof, in which for example the two or more capacitive elements coupled in parallel may be substantial identical to form a capacitor bank, the two or more capacitive elements comprising different characteristic properties complementing each other such as a combination of a capacitor capable of fast repetitive charge and discharge cycles during a switching period associated with an operational switching frequency and a battery comprising a very high capacitance rating or a combination thereof, and in which a series coupling of the two or more capacitive elements may provide the means for bridging a higher voltage rating across the series coupling.

According to each of the at least two auxiliary units included in the crosswise switching charge pump setting the high side capacitance section may comprise a capacitive element being one of the at least one capacitive element, a resistive element coupled in series or coupled in parallel with the capacitive element, an inductive element coupled in series or coupled in parallel with the capacitive element or a combination thereof, and the low side capacitance section may comprise a capacitive element being one of the at least one capacitive element, a resistive element coupled in series or coupled in parallel with the capacitive element, an inductive element coupled in series or coupled in parallel with the capacitive element or a combination thereof. As an example the high side capacitance section and the low side capacitance section may include each a parallel coupling of a first branch comprising a resistive element coupled in series with a ceramic capacitor and a second branch comprising an inductive element coupled in series with an electrolytic capacitor to form a R/L snubber. As a further example two or more capacitive elements being two or more of the at least one capacitive element of the high side capacitance section or being two or more of the at least one capacitive element of the low side capacitance section may be coupled in series, in which each of the two or more capacitive elements may be coupled in parallel with a resistive element for balancing means as well as for discharging means during a shut-down phase. A resistive element included in the high side capacitance section or included in the low side capacitance section may be for example a resistor, a thick film resistor, a carbon resistor, a metal film resistor, a SMT resistor, a printed conductive polymer paste resistor on a printed circuit board (PCB), ESR (Equivalent Series Resistance) or a combination of resistive elements whereas an inductive element may be for example an inductor, a ferrite bead, a

10

15

20

25

30

35

wire wound ceramic inductor, a SMT shielded power inductor, inductance of a track on a PCB, ESL (Equivalent Series Inductance) or a combination of inductive elements.

According to the crosswise switching charge pump setting implemented with the at least two auxiliary units and the at least one interlace unit the crosswise switching charge pump setting may comprise a parallel coupling of two or more of the at least two auxiliary units to form a cluster. The parallel coupling of the two or more of the at least two auxiliary units to form the cluster may be implemented by means of the high side terminals coupled, the common side terminals coupled and the low side terminals coupled of the two or more of the at least two auxiliary units.

Furthermore according to the crosswise switching charge pump setting implemented with the at least two auxiliary units and the at least one interlace unit the common side terminal in particular of each of the at least two auxiliary units may be capable to provide a reference voltage, to provide the means for a coupling with for example a load, to provide the means for a coupling of the switching power converter system or a combination thereof.

According to the H8H topology 800 the interlace unit 504 is operable to couple in response to one or more of the at least one pulse modulated control signal the auxiliary unit being pre-coupled 502 with the auxiliary unit being post-coupled 506 repetitively in accordance with the high operational state and the low operational state of the interlace unit, in which a pulse modulated control signal being one of the at least one pulse modulated control signal comprises a switching period associated with an operational switching frequency of the interlace unit. Subsequently the switching period of the pulse modulated control signal may be subdivided in a first period portion and a second period portion by means of a first switched transition and a second switched transition, in which the first period portion initiated by means of the first switched transition may be associated with a generation as well as a duration of the high operational state of the interlace unit, and in which the second period portion initiated by means of the second switched transition may be associated with a generation as well as a duration of the low operational state of the interlace unit.

According to the H8H topology 800 formed by means of the configuration of the interlace unit 504 intermediately coupled in cascade with the auxiliary unit being pre-coupled 502 and the auxiliary unit being post-coupled 506 the interlace unit may be basically implemented with two circuit settings each being operable to couple in response to one or more of the at least one pulse modulated control signal the auxiliary unit being pre-coupled with the auxiliary unit being post-coupled repetitively in accordance with the high operational state and the low operational state of the interlace unit, in which Figure 5 illustrates the H8H topology

10

15

20

25

30

35

comprising a first circuit setting of the interlace unit being preferred, and in which Figure 6 illustrates the H8H topology comprising a second circuit setting of the interlace unit being an alternative. Furthermore the Figures 5C and 5D illustrate the configuration of the H8H topology, in which the auxiliary unit being pre-coupled 502, the auxiliary unit being post-coupled 506 and the interlace unit 504 are adapted in accordance with a variation of a circuit diagram as shown in Figure 5. The variation may be applicable to a circuit diagram as shown in Figure 6 as well in an analogous manner.

According to the first circuit setting of the interlace unit 504 intermediately coupled in cascade with the auxiliary unit being pre-coupled 502 and the auxiliary unit being post-coupled 506 to form the H8H topology 800 as shown in Figure 5 the first circuit setting being preferred may be constituted with a first circuit branch B1 and a second circuit branch B2, in which the first circuit branch B1 and the second circuit branch B2 comprise each at least one high side switching element SH, QH and at least one low side switching element SL, QL coupled in series. Subsequently according to the second circuit branch B2 the at least one high side switching element QH is coupled between a high post side terminal G4 and an access terminal Q4 of the interlace unit, and the at least one low side switching element QL is coupled between the access terminal Q4 and a low post side terminal K4 of the interlace unit, and according to the first circuit branch B1 the at least one high side switching element SH is coupled between a high pre side terminal D4 and an interlink terminal S4 of the interlace unit, and the at least one low side switching element SL is coupled between the interlink terminal S4 and a low pre side terminal F4 of the interlace unit. In addition in accordance with the configuration to form the H8H topology 800 as shown in Figure 5 the high post side terminal G4 may be coupled to the high side terminal H6 of the auxiliary unit being post-coupled, the access terminal Q4 may be coupled to the common side terminal C2 of the auxiliary unit being pre-coupled, the low post side terminal K4 may be coupled to the low side terminal L6 of the auxiliary unit being post-coupled, the high pre side terminal D4 may be coupled to the high side terminal H2 of the auxiliary unit being pre-coupled, the interlink terminal S4 may be coupled to the common side terminal C6 of the auxiliary unit being post-coupled, and the low pre side terminal F4 may be coupled to low side terminal L2 of the auxiliary unit being pre-coupled. Consequently in accordance with the first circuit setting of the interlace unit 504 intermediately coupled in cascade with the auxiliary unit being pre-coupled 502 and the auxiliary unit being post-coupled 506 to form the H8H topology 800 as shown in Figure 5 the interlace unit being preferred is operable to couple in response to one or more of the at least one pulse modulated control signal the auxiliary unit being pre-coupled with the auxiliary unit being post-coupled repetitively in accordance with the

10

15

20

25

30

35

high operational state and the low operational state of the interlace unit, in which during the high operational state the high side terminal H2 of the auxiliary unit being pre-coupled may be coupled with the common side terminal C6 of the auxiliary unit being post-coupled and the common side terminal C2 of the auxiliary unit being pre-coupled may be coupled with the low side terminal L6 of the auxiliary unit being post-coupled by means of the at least one high side switching element SH of the first circuit branch B1 as well as the at least one low side switching element QL of the second circuit branch B2 being conductive in accordance with the high operational state and the at least one low side switching element SL of the first circuit branch as well as the at least one high side switching element QH of the second circuit branch being nonconductive in accordance with the high operational state, and in which during the low operational state the common side terminal C2 of the auxiliary unit being pre-coupled may be coupled with the high side terminal H6 of the auxiliary unit being post-coupled and the low side terminal L2 of the auxiliary unit being pre-coupled may be coupled with the common side terminal C6 of the auxiliary unit being post-coupled by means of the at least one low side switching element SL of the first circuit branch as well as the at least one high side switching element QH of the second circuit branch being conductive in accordance with the low operational state and the at least one high side switching element SH of the first circuit branch as well as the at least one low side switching element QL of the second circuit branch being nonconductive in accordance with the low operational state.

According to the first circuit setting of the interlace unit 504 as shown in Figure 5 responsive to one or more of the at least one pulse modulated control signal to generate the high operational state and the low operational state of the interlace unit repetitively the at least one high side switching element SH, QH and the at least one low side switching element SL, QL of both the first circuit branch B1 and the second circuit branch B2 may be constituted with actively driven semiconductors, in which an actively driven semiconductor being one of the actively driven semiconductors may be responsive to a pulse modulated control signal being one of the at least one pulse modulated control signal. As an example each of the actively driven semiconductors SH, SL, QH, QL included in the first circuit branch B1 and the second circuit branch B2 of the first circuit setting of the interlace unit 504 as shown in Figure 5A may be implemented with a MOSFET responsive to a pulse modulated control signal being one of the at least one pulse modulated control signal. Alternatively the at least one high side switching element QH and the at least one low side switching element QL of the second circuit branch B2 are constituted with passively driven semiconductors QH, QL, and the at least one high side switching element SH and the at least one low side switching element SL of the first circuit

10

15

20

25

30

35

branch B1 are constituted with actively driven semiconductors SH, SL, in which an actively driven semiconductor being one of the actively driven semiconductors may be responsive to a pulse modulated control signal being one of the at least one pulse modulated control signal. As an example each of the passively driven semiconductors QH, QL included in the second circuit branch B2 of the first circuit setting of the interlace unit 504 as shown in Figure 5B may be implemented with a DIODE and each of the actively driven semiconductors SH, SL included in the first circuit branch B1 of the first circuit setting of the interlace unit 504 as shown in Figure 5B may be implemented with a MOSFET responsive to a pulse modulated control signal being one of the at least one pulse modulated control signal.

According to the second circuit setting of the interlace unit 504 intermediately coupled in cascade with the auxiliary unit being pre-coupled 502 and the auxiliary unit being post-coupled 506 to form the H8H topology 800 as shown in Figure 6 the second circuit setting being the alternative may be constituted with a first circuit branch B1 and a second circuit branch B2, in which the first circuit branch and the second circuit branch comprise each at least one high side switching element QH, SH, at least one mid high side switching element HS, HQ, at least one mid low side switching element LS, LQ and at least one low side switching element QL, SL coupled in series in this order. Subsequently according to the second circuit branch B2 the at least one high side switching element SH is coupled between the high pre side terminal D4 and a common high side terminal H4 of the interlace unit 504, the at least one mid high side switching element HQ is coupled between the common high side terminal H4 and the access terminal Q4 of the interlace unit, the at least one mid low side switching element LQ is coupled between the access terminal Q4 and a common low side terminal L4 of the interlace unit, and the at least one low side switching element SL is coupled between the common low side terminal L4 and the low pre side terminal F4 of the interlace unit, and according to the first circuit branch B1 the at least one high side switching element QH is coupled between the high post side terminal G4 and the common high side terminal H4 of the interlace unit, the at least one mid high side switching element HS is coupled between the common high side terminal H4 and the interlink terminal S4 of the interlace unit, the at least one mid low side switching element LS is coupled between the interlink terminal S4 and the common low side terminal L4 of the interlace unit, and the at least one low side switching element QL is coupled between the common low side terminal L4 and the low post side terminal K4 of the interlace unit. In addition in accordance with the configuration to form the H8H topology 800 as shown in Figure 6 the high post side terminal G4 may be coupled to the high side terminal H6 of the auxiliary unit being post-coupled, the access terminal Q4 may be coupled to the common side terminal C2 of the auxiliary unit being pre-

coupled, the low post side terminal K4 may be coupled to the low side terminal L6 of the 5 auxiliary unit being post-coupled, the high pre side terminal D4 may be coupled to the high side terminal H2 of the auxiliary unit being pre-coupled, the interlink terminal S4 may be coupled to the common side terminal C6 of the auxiliary unit being post-coupled, and the low pre side terminal F4 may be coupled to low side terminal L2 of the auxiliary unit being pre-coupled. 10 Consequently in accordance with the second circuit setting of the interlace unit 504 intermediately coupled in cascade with the auxiliary unit being pre-coupled 502 and the auxiliary unit being post-coupled 506 to form the H8H topology 800 as shown in Figure 6 the interlace unit being the alternative is operable to couple in response to one or more of the at least one pulse modulated control signal the auxiliary unit being pre-coupled with the auxiliary unit being post-coupled repetitively in accordance with the high operational state and the low operational 15 state of the interlace unit, in which during the high operational state the high side terminal H2 of the auxiliary unit being pre-coupled may be coupled with the common side terminal C6 of the auxiliary unit being post-coupled and the common side terminal C2 of the auxiliary unit being pre-coupled may be coupled with the low side terminal L6 of the auxiliary unit being postcoupled by means of the at least one high side switching element SH of the second circuit 20 branch, the at least one mid low side switching element LQ of the second circuit branch, the at least one mid high side switching element HS of the first circuit branch as well as the at least one low side switching element QL of the first circuit branch being conductive in accordance with the high operational state, and the at least one mid high side switching element HQ of the second 25 circuit branch, the at least one low side switching element SL of the second circuit branch, the at least one high side switching element QH of the first circuit branch as well as the at least one mid low side switching element LS of the first circuit branch being non-conductive in accordance with the high operational state, and in which during the low operational state the common side terminal C2 of the auxiliary unit being pre-coupled may be coupled with the high 30 side terminal H6 of the auxiliary unit being post-coupled and the low side terminal L2 of the auxiliary unit being pre-coupled may be coupled with the common side terminal C6 of the auxiliary unit being post-coupled by means of the at least one mid high side switching element HQ of the second circuit branch, the at least one low side switching element SL of the second circuit branch, the at least one high side switching element QH of the first circuit branch as well as the at least one mid low side switching element LS of the first circuit branch being conductive 35 in accordance with the low operational state, and the at least one high side switching element SH of the second circuit branch, the at least one mid low side switching element LQ of the second circuit branch, the at least one mid high side switching element HS of the first circuit branch as

10

15

20

25

30

35

well as the at least one low side switching element QL of the first circuit branch being non-conductive in accordance with the low operational state.