# (11) EP 2 215 856 B1

### (12)

# **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention of the grant of the patent: 27.02.2019 Bulletin 2019/09

(21) Application number: 07851867.7

(22) Date of filing: 29.11.2007

(51) Int Cl.: H04R 19/02 (2006.01)

(86) International application number: PCT/NL2007/050607

(87) International publication number: WO 2009/070004 (04.06.2009 Gazette 2009/23)

# (54) AN ELECTROSTATIC SPEAKER SYSTEM

ELEKTRTOSTATISCHES LAUTSPRECHER SYSTEM SYSTÈME DE HAUT-PARLEUR ÉLECTROSTATIQUE

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE

SI SK TR

- (43) Date of publication of application: 11.08.2010 Bulletin 2010/32

- (73) Proprietor: Hiensch Innovations B.V. 6881 ME Velp (NL)

- (72) Inventor: Hiensch, Henk-Albert 6881 ME Velp (NL)

- (74) Representative: de Hoog, Johannes Hendrik

Octrooibureau de Hoog

Gouverneurslaan 18 A

3905 HE Veenendaal (NL)

- (56) References cited: WO-A-2007/081584 US-A- 5 352 986

P 2 215 856 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

### Description

30

35

50

#### Field of the invention

[0001] The invention relates an electrostatic speaker system, and more specifically, to an electrostatic speaker system comprising a pulse modulator, a high voltage switching output stage amplifying the pulse modulated signal and an extraction filter demodulating the amplified pulse modulated high voltage signal, a filter for attenuating high frequencies of the amplified pulse modulated high voltage signal and an electrostatic speaker element coupled to an output of the filter.

### Description of the Related and Prior Art

[0002] An electrostatic speaker element utilizes the electrostatic principle in order to generate an acoustic signal. For example, the most common embodiment of an electrostatic speaker element comprises two electrical conductive and perforated plates, also known as the stators and in addition a thin electrical conductive diaphragm disposed between the two stators with on either side a small air gap with respect to the stators. Subsequently the electrical conductive diaphragm will be held on a constant electrical charge with respect to the stators by means of a high DC bias voltage in order to meet the desired electrical field strength. The stators are connected to an AC high voltage analogue signal, in which the stators will be driven in counter phase, also called a "push pull" configuration, resulting in a proportional and uniform electrostatic field between both stators, which generates sufficient field strength in order to cause a force on the electrical charged diaphragm, providing movement of the diaphragm and subsequently the surrounding air. In contrast to the electro dynamic cone speaker, which is a low impedance device, an electrostatic speaker will yield a capacitive load exhibiting a high impedance device.

**[0003]** In order to reproduce an acoustical source signal, a modular system of components may be required, in which each component provides a specific functionality.

[0004] In general such a modular system, constituted with an electrostatic speaker system, is made up of the following components, namely,

- An audio reproduction device, such as for example a CD player.

- An audio power amplifier providing gain to an audio signal in order to drive a low impedance device, such as for example an electro dynamic cone speaker.

- An audio power transformer performing the necessary impedance matching in order to drive a high impedance device, namely the capacitive load of an electrostatic speaker element, in which the audio power transformer converts the low AC voltage signal into an AC high voltage analogue signal.

- An electrostatic speaker element driven with the AC high voltage analogue signal derived from the audio power transformer, resulting in for example an alternating electrical field between the stators, in which the electrical charged diaphragm will follow.

**[0005]** The secondary side of an audio power transformer, connected to an electrostatic speaker element, may result in very low and a complex impedance on the primary side of the transformer connected to an audio power amplifier as described above. Therefore the audio power amplifier may not perform well as designed, due to the very low and complex impedance, resulting in increased distortion products and the possibility of instable and perturbing behaviour. As a result a stable and very powerful audio amplifier may be necessary.

[0006] The key role of an audio power transformer is to provide a constant transformation ratio over the total operational audio bandwidth. The combination of leak inductance and the parasitic capacitance, arising from the secondary layer windings of a power transformer, in conjunction with the capacitive load of a connected electrostatic speaker element results in a LC low pass filter, which may define the frequency response negatively. The power handling is another limiting factor in the configuration of an audio power transformer, due to a mix of properties. As a result the construction of an audio power transformer is critical, because the necessity for a compromise between the diversity of properties is inevitable. Furthermore the constituted electrostatic speaker element in conjunction with an audio power transformer will be designed towards a standard audio power amplifier, resulting in a narrowed flexibility of design, construction and optimization possibilities. Subsequently it is apparent that an audio power transformer has physical limitations in an approach that allows driving an electrostatic speaker element.

[0007] To overcome the deficiencies of driving an electrostatic speaker element with a standard audio power amplifier in conjunction with a power transformer, there can be taken advantage of a high voltage audio power amplifier, which is capable of driving the capacitive load of an electrostatic speaker element directly, without the use of a power transformer. A high voltage audio power amplifier designed in order to drive a capacitive load of an electrostatic speaker element directly, is in principle better than driving an electrostatic speaker element with a standard audio power amplifier in conjunction with a power transformer. A high voltage audio power amplifier may be constituted with the use of semi-

conductor technology or thermionic valves technology (Vacuum tubes).

[0008] The diversity of semi-conductor based active components, such as for example a Bipolar Junction Transistor (BJT), a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) or an Insulated Gate Bipolar Junction Transistor (IGBT), can be connected in series in order to meet the desired AC high voltage output signal, in which the bridged voltage may be divided equally across the constituted semi-conductors. A high voltage audio power amplifier, designed with the use of class-A/B technology, has two basic flaws namely bias current adjustment and power dissipation. In order to reduce cross over distortion employing class-A/B technology, bias current adjustment will be required, in which the optimum will be achieved in a class-A setting. As a result of an increasing bias current in order to reduce cross over distortion, the power dissipation will increase accordingly. Subsequently a class-A setting will be difficult to obtain in an embodiment of a high voltage audio power amplifier, because of the resulting heavy power requirements. In addition, by employing a complex load, such as the capacitive load of an electrostatic speaker element, the power dissipation will increase further as well as the possibility of instable behaviour. Therefore this concept has no optimum, which implicates a compromise.

**[0009]** Another option in order to constitute a high voltage audio power amplifier is the use of thermionic valves technology (vacuum tubes) as mentioned above. In general, employing thermionic valves technology has additional drawbacks with respect to semi-conductor technology as described above, such as for example the sensitivity for ageing and the relatively poor reliability.

**[0010]** As described above, the diversity of prior art amplification techniques have much in common related to the driving capability of a capacitive load, namely,

- Feedback and a high bias current are necessary in order to aim at a linear transfer;

- Stability is limited by employing a capacitive load;

- Very low energy efficiency:

- Further increase of power dissipation by employing a capacitive load;

- High variance of temperature and therefore a shift of parameters;

- Expensive due to a high energetic power supply and cooling means.

**[0011]** A switching audio amplifier also called a pulse modulation amplifier and more specific called for example a pulse width modulation amplifier or a class-D amplifier, forms, with respect to energy efficiency and the interrelated subjects, an exception to the low voltage amplification concepts capable of driving a low impedance device, such as for example an electro dynamic cone speaker as described above. The concept of a switching amplifier may achieve an efficiency of 90% and higher, which is inherent to the principle. WO00072627 A1 discloses a switching amplifier driving a capacitive transducer.

# 35 Summary of the invention

**[0012]** According to the above stated deficiencies that exist with prior art arrangements, the objective of the present invention is to provide an improved electrostatic speaker system, which is capable of driving a capacitive load of an electrostatic speaker element directly showing a high level of quality in sound reproduction.

[0013] The present invention provides an electrostatic speaker system according to claim 1 and a method for driving a respective electrostatic speaker element according to claim 11. Further embodiments are defined in the dependent claims.

[0014] According to the present invention, the electrostatic speaker system comprises:

- a high voltage switching power amplifier,

- an extraction filter having an input coupled to an output of the high voltage switching amplifier, and

- an electrostatic speaker element having a capacitive load and an input coupled to an output of the extraction filter, wherein the combination of the extraction filter and capacitive load form a filter circuitry having at least a first filter stage and a second filter stage,

the first filter stage comprising a RLC circuit having a resonant frequency  $\omega 0$  and a quality factor Q > 1/2 and the second filter stage being a low pass filter having at least one electrical element for damping a signal component at the resonant frequency  $\omega 0$  of the RLC circuit at the output of the extraction filter.

[0015] The present invention provides a system of driving the capacitive load of an electrostatic speaker element directly allowing a wide operational bandwidth with a flat frequency response, stability, reliability, flexibility, and a very energy efficient concept, in which the amplified analogue AC high voltage signal can be processed very precise obtaining high fidelity. Furthermore the approach of the present invention allowing a very energy efficient concept may result in a low energetic power supply, less cooling means and therefore smaller enclosing means and in addition a low temperature

20

25

50

variance resulting in a low shift of parameters and a long life cycle of the resided components.

[0016] The objective of the invention is a well designed extraction filter obtained in accordance with the presented methods, circuitry, equations and components in the manner described later, in which the extraction filter may act as a passive integrator, provided that the frequency of the pulse modulated switching signal presented at the input of the extraction filter is at least an order of magnitude higher with respect to the operational bandwidth of the extraction filter. Subsequently the analogue AC output signal, defined within the operation bandwidth of the extraction filter, is equal to the average value of the pulse modulated switching input signal, wherein the amplified analogue AC output signal will be the proportional replica of the analogue source signal. The capacitive load of an electrostatic speaker element, connected to the output of the extraction filter, will form an integral part of the extraction filter configuration in order to obtain an approach that allows in the frequency domain as well as in the signal domain a wide operational bandwidth with a flat frequency response, a narrow filter roll-off with sufficient attenuation of the switching frequency and its harmonics, good impulse response, stable, in which the analogue signal will be reconstructed very precise.

**[0017]** Furthermore the invention provides an approach of segmenting an electrostatic speaker element electrically in conjunction with an extraction filter and therefore providing a technique that allows adapting the electrostatic speaker element acoustically.

[0018] Further embodiments of the invention are indicated by the dependent claims.

[0019] Based on the discussion given in the present invention, the open loop characteristics of a high voltage switching power amplifier, connected to the capacitive load of an electrostatic speaker element, may be very good in order to obtain a high level of quality in sound reproduction. This novel approach of the preferred embodiment will be achieved by means of a highly alleviated and subsequently very stable high voltage power supply providing high resolution voltage levels and therefore exhibiting very low Total Harmonic Distortion (THD) characteristics, obtained in accordance with an employed high impedance device as a load, the implemented high efficient switching topology, and a high reactive power component inherent to a capacitive load, in which the reactive energy may be regenerated in conjunction with the extraction filter and the high voltage DC power supply. In addition very fast switching of the high voltage switching output stage may be accomplished with a minimum of dead time by means of driving a high impedance device, in which the high impedance device will comprise an extraction filter including the capacitive load. Furthermore a well designed extraction filter may conduce to very good open loop characteristics of the preferred high voltage switching power amplifier. As a result the present invention provides a digital front end high voltage switching power amplifier driving the capacitive load of an electrostatic speaker element, without the use of any feedback means.

[0020] In general a designer, employing the present invention, is provided with the flexibility in choosing the various operating topologies as will be presented hereinafter in order to match the desired parameters of an electrostatic speaker setting. Subsequently it is to be noted that an embodiment of a high voltage switching power amplifier in the scope of the present invention is capable of operating at various high voltage levels in conjunction with various power levels, at various performance levels, with various pulse modulation techniques in conjunction with various analogues and digital input formats, with various output stage switching topologies, and with various extraction filter configurations.

# Short description of drawings

30

35

45

50

55

**[0021]** The present invention will be discussed in more detail below, using a number of exemplary embodiments, with reference to the attached drawings that are intended to illustrate the invention but not to limit its scope which is defined by the annexed claims and its equivalent embodiment, in which

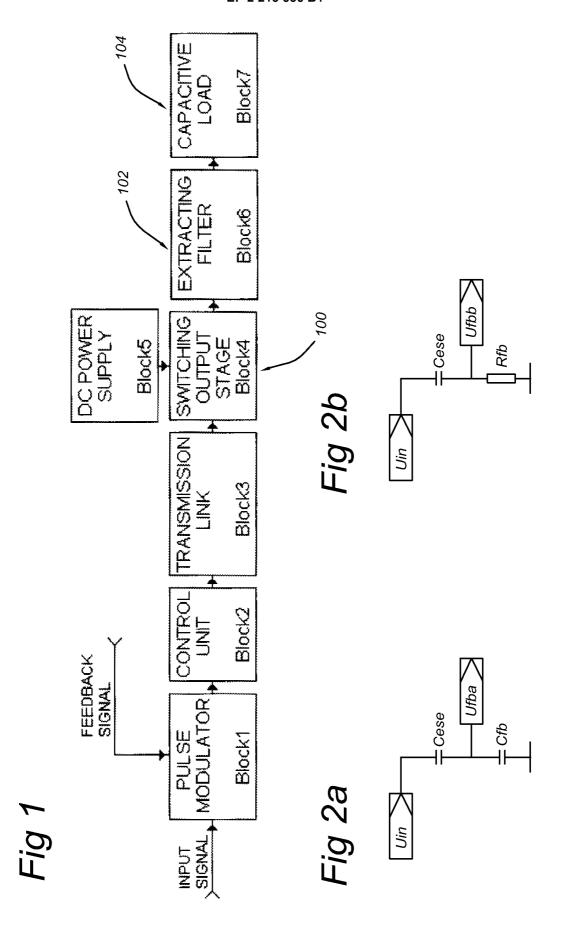

Figure 1 illustrates a conceptual block diagram of an electrostatic speaker system according to the invention,

Figure 2a illustrates an electrical circuit diagram of a voltage feedback signal,

Figure 2b illustrates an electrical circuit diagram of a current feedback signal,

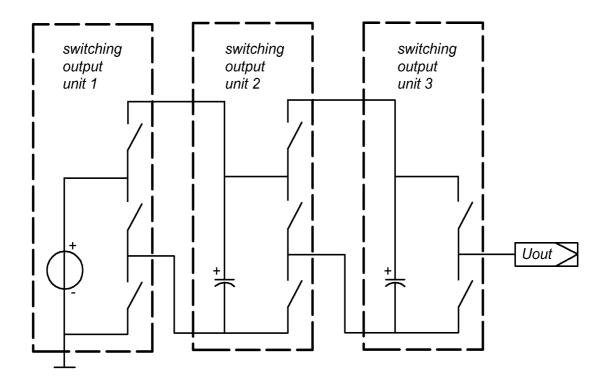

Figure 3a illustrates the circuit configuration of a gradient switching power topology,

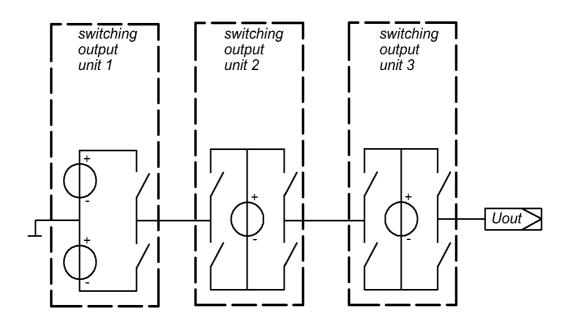

Figure 3b illustrates the circuit configuration of a more complex gradient switching power topology,

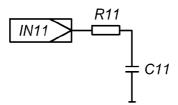

Figure 4 illustrates a simple passive single ended low pass first order filter,

Figure 5 illustrates a passive differential low pass first order filter,

Figure 6 illustrates a single ended low pass second order filter,

Figure 7 illustrates a differential low pass second order filter,

Figure 8 illustrates a single ended low pass third order filter,

Figure 9 illustrates a differential low pass third order filter,

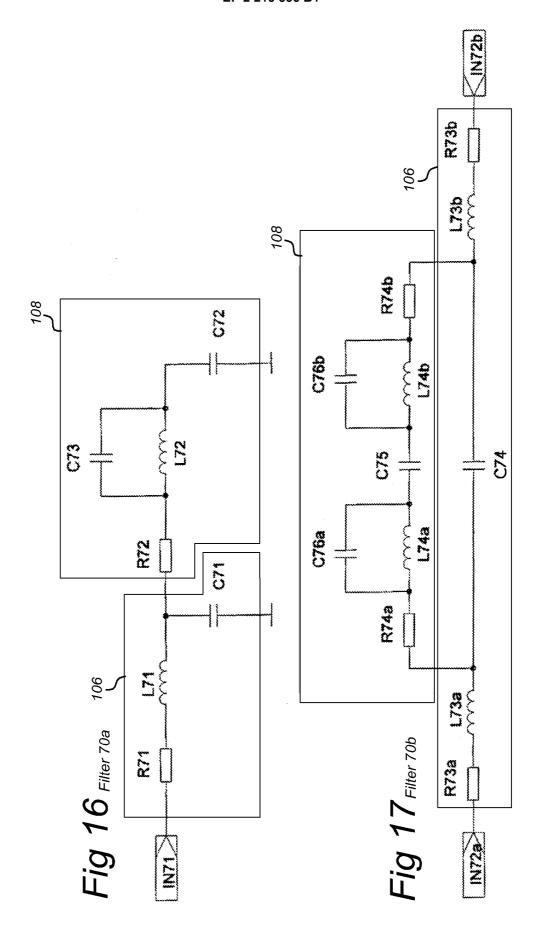

Figure 10 illustrates a single ended low pass third order filter in another form,

Figure 11 illustrates a differential low pass third order filter in another form,

Figure 12 illustrates a single ended low pass fourth order filter,

Figure 13 illustrates a differential low pass fourth order filter,

Figure 14 illustrates the preferred single ended extraction filter embodiment,

- Figure 15 illustrates the preferred differential extraction filter embodiment,

- Figure 16 illustrates the preferred single ended extraction filter supplemented with a parallel resonant filter,

- Figure 17 illustrates the preferred differential extraction filter supplemented with two parallel resonant filters,

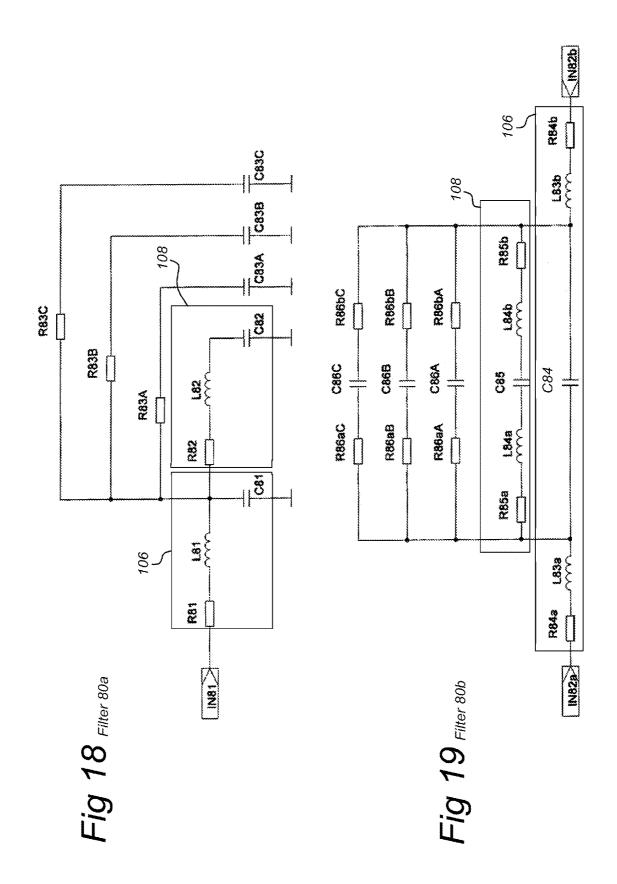

- Figure 18 illustrates the preferred single ended extraction filter supplemented with one or several further low pass filters being parallel connected to the main second filter stage,

- Figure 19 illustrates the preferred differential extraction filter supplemented with one or several further low pass filters being parallel connected to the main second filter stage, and

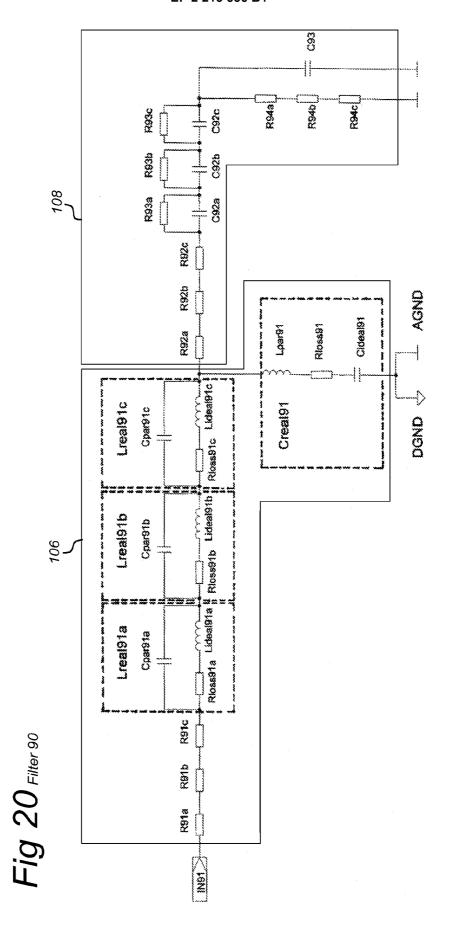

- Figure 20 illustrates a more practical circuit configuration of a single ended band pass filter comprising a high pass first order filter in conjunction with a low pass third order filter.

# Detailed description of exemplary embodiments

5

10

30

50

**[0022]** A basic conceptual block structure of an electrostatic speaker system is shown in Figure 1, comprising a pulse modulator (Block1), a control unit (Block2), a transmission link (Block3), a high voltage switching output stage (Block4), a high voltage DC power supply (Block5), an extraction filter (Block6) and a capacitive load (Block7).

**[0023]** The invention provides an embodiment that may receive one or several analogue audio signals as well as digital audio signals as an input, emanated from for example a pre-amplifier or an audio reproduction device, such as a CD player, and connected to a pulse modulator Figure 1; Block1. The digital audio signal can be in any suitable digital audio format such as: SPDIF, AAC, DTS, Quicktime, WMA, MP3.

**[0024]** For example, a pulse modulator and more specific a Pulse Width Modulator (PWM) is provided with an analogue audio formatted input signal and a reference triangular signal, in which the frequency of the reference triangular signal is at least an order of magnitude higher with respect to the operational bandwidth of the analogue audio formatted input signal. Subsequently the pulse width modulator will convert the analogue audio formatted input signal, by comparison of the analogue input signal with the reference triangular signal in an analogue way, into a pulse width modulated signal exhibiting a fundamental equal to the triangular signal frequency, in which the average value of the pulse modulated signal will be the equivalent of the analogue audio formatted input signal.

[0025] The pulse modulation technique is not limited to straight pulse width modulation as described in an example above and includes other pulse modulation means optimized for audio applications, such as an analogue or digital pulse modulator employing a multi-bit pulse modulated topology as will be described below in more detail. A pulse modulation topology Figure 1: Block1 may be configured for compensating the characteristic corresponding to a feedback signal, which feeds back the condition of for example the switching output stage in order to obviate distortion due to timing errors.

**[0026]** The capacitive load of an electrostatic speaker element may provide feedback to a pulse modulation topology as well, based on voltage feedback as well as current feedback.

[0027] As illustrated in Figure 2a, an input terminal Uin may receive a ground referenced AC high voltage analogue signal and is connected to the capacitive load Cese of an electrostatic speaker element that is series connected to a ground referenced capacitor Cfb providing a ground referenced voltage feedback signal Ufba, in which the capacitive load Cese will form a capacitive voltage divider with respect to a much higher capacitance valued capacitor Cfb in order to set a proper feedback ratio. As illustrated in Figure 2b, an input terminal Uin may receive a ground referenced AC high voltage analogue signal and is connected to the capacitive load Cese of an electrostatic speaker element that is series connected to a ground referenced resistor Rfb providing a ground referenced current feedback signal Ufbb, in which the feedback signal Ufbb will be the equivalent ratio of the current flowing through the capacitive load Cese.

[0028] It is to be noted, that the designer, employing the invention, is provided with the flexibility in choosing the various pulse modulation topologies, such as for example sigma delta modulation, self oscillating class D modulation or a digital modulator like Equibit from Texas Instruments and class Z from Zetex. Furthermore the various pulse modulation topologies may be combined in conjunction with feed forward means as well as feedback means implemented in the analogue domain as well as in the digital domain.

[0029] An electrostatic speaker system according to the invention could optionally comprise a control unit Block 2 implementing for example a delay timing control and a limiter function, due to the practical limitations of the components constituted in a switching power topology. In general a delay timing control will adjust the timing of the pulse modulated signal generated by the modulator, in which the adjusted time, called dead time, avoids cross conduction during transition in the switching output stage. Furthermore the pulse width of the pulse modulated signal can be limited to be within an acceptable minimum pulse width by means of a limiter function in order to obtain save operation of the switching output stage.

**[0030]** The control unit Block 2 is not limited to the examples of the feed forward control methods as described above and could include other control means, such as feedback means, which eliminates errors resulting in a more efficient and reliable operation of the electrostatic speaker system.

[0031] In general a switching power topology exhibits a circuit configuration of one or several switching elements, wherein these switching elements may be floating with respect to each other as well as other enclosed components

including a ground reference. Subsequently there may be taken advantage of one or several galvanically decoupled transmission links as shown in Figure 1; Block3 for each switching element in order to drive the constituted switching elements maintaining the floating properties. For example a galvanically decoupled transmission link may comprise a transmitter, constituted of a light emitting diode with an enclosed driver circuit, provided with a one-bit digital signal as an input, wherein the transmitter may be connected by means of an optic cable to a suitable receiver, such as a phototransistor enclosed in an driver circuit. Subsequently the receiver will be capable of driving a switching element in either a conductive or in a blocked condition corresponding to the one-bit digital input signal.

**[0032]** The galvanically decoupled transmission technique used is not limited to the example of a data transmission link as described above and could include other galvanic separation means, such as an integrated opto-isolator or a transformer, which are optimized for high speed in conjunction with high voltage operation. It is to be noted that the accuracy of the galvanically decoupled driver arrangement will be very important to the end system performance.

[0033] It is desired to employ a gradient switching topology as a switching power output stage Block4 in order to provide a stable and reliable method capable of generating a high voltage switching output signal. The high voltage switching output signal could have an output voltage on the order of magnitude from a few hundred up to a few thousand volts and will exhibit in addition high efficiency, which is inherent to the principle. In general a gradient switching power topology exhibits a well known method by one skilled in the art, wherein a number of cascaded switching output units will result in a switching output voltage, which may be the sum of voltages generated by the number of the switching output units, in which each switching output unit by itself may have a predetermined switching output voltage. By determining the output voltage of a switching output unit as well as selecting the number of the cascade connected switching output units, the desired maximum switching output voltage of a gradient switching output stage can be easily obtained. [0034] The switching power output stage implemented with a gradient switching power topology will enclose two or several switching output units, in which an output unit will comprise a plurality of switching elements, wherein a switching element may be any suitable type of semiconductor, such as for example a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) or a Bipolar Junction Transistor (BJT) in conjunction with a clamp diode. Furthermore each switching output unit will comprise a DC power supply which may be constituted of for example one suitable capacitor or more in parallel.

[0035] It is to be noted, that a gradient switching power topology can be implemented in various circuit configurations, of which two exemplary constituted circuits are shown in Figure 3a and Figure 3b. As illustrated in Figure 3a the circuit configuration of a gradient switching power topology will provide a switching output voltage equal to the summed voltages of the switching output units with respect to ground. Furthermore, the second and following DC power supplies of the cascaded switching output units will be charged by the main and initial DC power supply of the first switching output unit connected to ground. In the case a switching output signal without a DC voltage component is required with respect to ground, decoupling can be implemented by means of for example a DC blocking capacitor or a DC bias voltage. Referring to Figure 3b the circuit configuration of a more complex gradient switching power topology is shown providing a switching output signal without a DC voltage offset component with respect to ground. In addition each switching output unit may be implemented with a characteristic switching output voltage by means of an adapted DC power supply voltage.

30

50

**[0036]** In the case a gradient switching arrangement is constituted in a modular form in contradiction to an integrated approach, each implemented module can provide a switching output unit as described above supplemented with for example connector means as well as enclosure means and cooling means resulting in increased system versatility in choosing for example the desired switching output voltage or the resolution in voltage output steps by selecting the number of the switching output modules cascaded in a stacked form. Furthermore increased system versatility by means of a modular design may allow optimum cost to performance ratios with respect to the production of a high voltage switching amplifier.

[0037] It is to be noted, that each switching output unit of a gradient switching arrangement, separate and yet interrelated multi-bit pulse modulated control schemes may be implemented, in order to provide a combination of switching output voltages and currents at different levels, in which each switching output unit independently of one another can be switched at different times and frequencies, provided that the switching frequency of at least one switching output unit is at least an order of magnitude higher with respect to the analogue operational signal bandwidth. A gradient switching arrangement employing multi-bit pulse modulated control schemes as described above may be used for example to optimize filtering performance in order to enhance extracting a high voltage analogue signal from the multi-bit pulse modulated high voltage switching signal.

[0038] The gradient switching power topologies according to the exemplary circuit configurations shown in Figure 3a and Figure 3b illustrate a half bridge topology.

**[0039]** However in other presented embodiments of the invention a full bridge or H bridge topology will be employed as well, in which two gradient switching arrangements are set on opposite sites of one another as described below in more detail.

[0040] The gradient switching power topology used in the preferred embodiment of the invention is not limited to the exemplary circuit configurations of the two gradient switching arrangements as described above and includes other

switching topology means, such as for example the most elementary well known switching half-bridge and full-bridge topologies, which are optimized for a well shaped block wave output signal and high voltage operation.

[0041] Considering the capacitive load of a high voltage power amplifier, the handled apparent power may consist of a dominant reactive power part over the real power part as will be described below in more detail. Subsequently it is an objective of a well designed high DC voltage power supply, indicated in Figure 1 by Block5, to handle the apparent power in order to drive the capacitive load of an electrostatic speaker element maintaining an accurate and stable DC voltage under varying load conditions, in which the high DC voltage of the power supply will obviate inter-modulation with the block wave output signal of the switching output stage and therefore the related analogue output signal to a desired minimum, which may result in very good total harmonic distortion (THD) characteristics even in an open loop setting in accordance with an employed high impedance device as a load, the constituted high efficient switching topology, and a high reactive power component inherent to a capacitive load.

**[0042]** A DC power supply deriving energy from the AC mains may be implemented by means of well-known design topologies such as for example a bridge rectifier in conjunction with one stabilizing capacitor or more in parallel or a switched mode power supply (SMPS).

**[0043]** In the case of a DC power supply, in which the DC voltage can be adjusted between zero and the maximum voltage, a main volume analogue output signal control will be obtained. Hence an analogue or digital audio formatted inputs signal maintaining maximum signal resolution throughout the circuitry of the high voltage switching power amplifier. As a result, small signal amplification will be improved, noise will be reduced and a further increase of efficiency will be obtained, with respect to for example regular main volume control of an analogue or digital audio formatted signal at the input of a high voltage switching power amplifier.

**[0044]** An objective of the invention is a well designed extraction filter, indicated in Figure 1 by Block6. Below some examples of extraction filter topologies will be described and the method how to derive the optimal component values for the respective extraction filter topologies. The presented methods, circuitry, equations and components enables a skilled person in the art to obtain an extraction filter that will exhibit two primary filtering requirements described hereinafter which provides in the frequency domain as well as in the signal domain a wide operational bandwidth with a flat frequency response, a narrow filter roll-off with sufficient attenuation of the switching frequency and its harmonics, a good impulse response, a stable filter, in which the analogue signal will be reconstructed very precise. It is to be noted, that the characteristic capacitive load of an electrostatic speaker element, indicated in Figure 1 by Block7, that is connected to the output of the extraction filter, will form an integral part of the extraction filter configuration in order to obtain the above stated objectives and will present in addition the starting point in extraction filter calculation. Therefore in the following description Block6 and Block7 are discussed simultaneously.

30

50

**[0045]** According to the first requirement, the extraction filter will be forced to act as a passive integrator, provided that the frequency of the generated high voltage switching output signal, typically between 250 kHz to 1.5 MHz, presented at the input of the extraction filter is at least an order of magnitude higher, typical a ratio factor between 5 and 10, with respect to the operational bandwidth of the extraction filter. Subsequently the analogue output signal, defined within the operation bandwidth of the extraction filter, is equal to the average value of the pulse modulated switching input signal, wherein the amplified analogue output signal will be the proportional replica of the analogue source signal.

[0046] According to the second requirement, the extraction filter will be forced to minimize electromagnetic interference (EMI), generated by the high voltage switching output stage. In general a high voltage output stage will provide a high voltage as well as a high frequency block wave signal with fast moving transient edges containing spectral energy at the switching frequency in conjunction with the integer multiples of the fundamental. As a result, an extraction filter is required, in which the switching frequency and its harmonics of the high voltage switching signal will be sufficient attenuated in order to minimize EMI from being radiated as well as conducted and in addition to guarantee compliance with applicable regulations.

**[0047]** For example Spread spectrum modulation can be employed in conjunction with an extraction filter in order to obtain proper EMI performance. In general spread spectrum modulation is obtained by dithering or randomizing the fundamental of a pulse modulated signal, rather than a fixed pulse modulated signal frequency. As a result the total amount of energy present in the frequency output spectrum of the extraction filter will remain the same employing spread spectrum modulation, but the total spectral energy is effectively spread out over a wider bandwidth and therefore not concentrated at a fixed switching frequency and its harmonics.

[0048] In general it is an objective to minimize electrical energy from being dissipated in the preferred extraction filter embodiment of the present invention. Furthermore the preferred extraction filter embodiment depends on various design issues in order to match the desired parameters, such as for example the design and construction of an electrostatic speaker element or the format of the pulse modulated signal that is being processed as will be covered by the present invention.

**[0049]** According to the basic construction of an electrostatic speaker element, comprising two electrical conductive and perforated stators and in addition a thin electrical conductive diaphragm disposed between the two stators with on either side a small air gap with respect to the stators, the resided capacitive load of an electrostatic speaker element

may be implemented in a single ended extraction filter configuration employing a half bridge switching topology as well as in a differential extraction filter configuration employing a full bridge switching topology. It is to be emphasised, that an employed differential extraction filter will be implemented symmetrical with respect to the capacitive load of an electrostatic speaker element in order to maintain the balance in the reversibly operating differential extraction filter.

[0050] In the case a single ended configuration is implemented, a half bridge switching topology will be used in conjunction with a single ended extraction filter, wherein the output of the single ended filter is connected to the electrical conductive diaphragm of the electrostatic speaker element. Furthermore both stators of the electrostatic speaker element are provided with a constant electrical charge complementing each other (a positive and a negative charge) with respect to the electrical conductive diaphragm. Subsequently the capacitive load of an electrostatic speaker element, implemented in a single ended configuration consists between the electrical conductive diaphragm and the two AC short circuited stators on either side of the diaphragm of the element.

**[0051]** In an alternative embodiment of an electrostatic speaker element, provided with a constant electrical charged diaphragm with respect to the stators, one of either stators may be driven in a single ended configuration with the other stator connected to for example a common DC reference voltage, in which the capacitive load will consist between the two stators of the element

**[0052]** However in another embodiment, a full bridge or H bridge switching topology may be employed in which two half bridge topologies are set on opposite sites of one another in order to drive the capacitive load of an electrostatic speaker element differentially by means of a differential extraction filter. In general the most elementary full bridge switching topology generates two block wave signals complementing each other, which results in an alternating differential voltage across the differential extraction filter providing twice the output voltage swing with respect to a half bridge topology employing the same supply voltage.

[0053] In the case a differential configuration is implemented, a full bridge switching topology will be used in conjunction with a differential extraction filter exhibiting a "push pull" configuration, wherein the output of the differential extraction filter is connected to the stators of the electrostatic speaker element. Furthermore the diaphragm of the electrostatic speaker element is provided with a constant electrical charge with respect to the stators. Subsequently the capacitive load of an electrostatic speaker element, implemented in a differential configuration consists between the stators of the element.

[0054] According to a single ended configuration as well as a differential configuration as described above each driving for example the capacitive load of an identical basic electrostatic speaker element, the resided capacitive load presented in a single ended configuration will be four times as heavy as the capacitive load resided in a differential configuration. As a result a basic electrostatic speaker element implemented in a single ended configuration requires one quarter of an employed analogue high voltage swing with respect to an identical electrostatic speaker element implemented in a differential configuration in order to generate an equal amount of electrical charge and subsequently equal electrical field strength.

30

50

[0055] It is to be noted, that a half bridge or a full bridge topology comprising a DC voltage offset component, due to for example a single supply voltage, than this DC voltage offset component can be obviated by means of for example a DC-blocking capacitor, a positive and negative supply voltage or a DC bias voltage, if an AC high voltage analogue signal without a DC voltage offset component is required, for example in conjunction with a common reference voltage implemented in a electrostatic speaker element. Similarly with the half bridge topology comprising a DC voltage offset component, the full bridge topology will have a DC voltage offset component on each side of the capacitive load with respect to a common reference voltage.

[0056] The diaphragm area of an electrostatic speaker element may be acoustically adapted by means of segmenting the diaphragm area into two or several segments, depending on the design and construction of the element in order to provide for example a wider disbursement of sound waves, in particular within the high frequency audible range. The approach that allows segmenting a diaphragm area acoustically can be obtained by segmenting one or both stators as well as the electrical conductive diaphragm area electrically. As a result each segment comprises a characteristic capacitance which will form the capacitive component employed in an extraction filter embodiment as described below in more detail. Needless to say that the segmentation technique implemented in an electrostatic speaker element may be employed in conjunction with a single ended configuration as well as a differential configuration as described above.

[0057] It is to be noted, that an electrostatic speaker element by itself may be interpreted as a segment as well with respect to for example another electrostatic speaker element. Furthermore the segmenting technique in order to adapt the operational bandwidth in whole or in part is not limited to an electrostatic speaker element and may include other audio projecting components, such as an electro dynamic cone speaker element. Nonetheless in the case an electrostatic speaker element is segmented in multiple sections in order to adapt the electrostatic speaker element acoustically, providing for example signal filter means or signal delay means, each segmented section by itself may be driven by a high voltage switching power amplifier, in which each of the multiple high voltage switching power amplifiers may be provided with an adapted analogue or digital formatted signal as an input distributed by an analogue or digital processing units enclosed in for example a pre-amplifier topology.

**[0058]** The following extraction filter embodiments of the present invention will now be described more specifically. It is to be emphasised, that the following descriptions of the present invention, with reference to the extraction filter embodiments, are presented herein for purpose of illustration and description only, in which the precise forms disclosed are not intended to be exhaustive or to be limited. Furthermore the extraction filter embodiments of the present invention resides not only in any filter configuration taken alone, but rather in the particular combination of all of its structures as well as all of its interrelationships for the functions specified.

[0059] Figure 4 illustrates the circuit diagram of single ended low pass filter 10a exhibiting a simple passive first order filter

**[0060]** As shown in Figure 4, the low pass filter 10a configuration may receive a high voltage pulse modulated signal provided at input terminal IN11 with respect to ground, wherein the filter 10a stage comprises a series connection of resistor R11 and capacitor C11, the series connection connected between the input terminal IN11 and a ground node. The constituted capacitor C11 in the low pass filter 10a configuration represents the capacitive load of an electrostatic speaker element.

[0061] Ideally the roll-off of the first order low pass filter 10a setting provides an attenuation of 20dB per decade after the cut-off frequency. The cut-off frequency expressed in radiant of filter 10a is

$$\omega_{filter I \theta u} = \frac{1}{R_{11} C_{11}} \tag{E1}$$

[0062] The output impedance of filter 10a is defined in accordance with the following

$$Z_{filter10a}(s) = \frac{R_{11}}{1 + s R_{11} C_{11}}$$

(E2)

and the transfer function of filter 10a is defined as

20

25

30

35

50

$$H_{filter10a}(s) = \frac{1}{1 + s R_{11} C_{11}}$$

(E3)

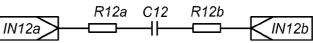

[0063] Figure 5 illustrates the circuit diagram of differential low pass filter 10b exhibiting a passive first order filter.

[0064] As shown in Figure 5, the low pass filter 10b configuration may receive a high voltage pulse modulated signal provided at input terminal IN12a with respect to a complemented high voltage pulse modulated signal provided at input terminal IN12b, wherein the filter 10b stage comprises a series connection of the first resistor R12a, capacitor C12 and the second resistor R12b, the series connection connected between the first input terminal IN12a and the second input terminal IN12b. The constituted capacitor C12 in the low pass filter 10b configuration represents the capacitive load of an electrostatic speaker element.

**[0065]** The differential filter 10b setting exhibits the equivalent model of the single ended filter 10a setting, which is implemented in another form. In order to match the filter characteristics of both the single ended filter 10a setting and the differential filter 10b setting, the resistance of resistor R11 is divided by 2, and assigned to the resistors R12a and R12b.

**[0066]** For example, if the resistor value of resistor R11 is calculated to be 10kOhm, then resistor R12a is set to 5kOhm and resistor R12b is set to 5kOhm. Finally the capacitance of capacitor C11 is equal to the capacitance of capacitor C12 representing the specified capacitive load.

**[0067]** The single ended filter 10a setting and the equivalent differential filter 10b setting are unconditionally stable, and may be employed for example in conjunction with other passive filter means of higher order as well as segmenting means. However, the single ended filter 10a and differential filter 10b configuration may not provide the extraction filter performance achieving the two stated primary filtering requirements as described above.

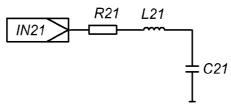

[0068] Figure 6 illustrates the circuit diagram of single ended low pass filter 20a exhibiting a passive second order RLC filter.

**[0069]** As shown in Figure 6, the low pass filter 20a configuration may receive a high voltage pulse modulated signal provided at input terminal IN21 with respect to ground, wherein the filter 20a stage comprises a series connection of resistor R21, inductor L21 and capacitor C21, the series connection connected between the input terminal IN21 and a ground node. The constituted capacitor C21 in the low pass filter 20a configuration represents the capacitive load of an electrostatic speaker element.

**[0070]** Ideally the roll-off of the low pass second order filter 20a setting provides an attenuation of 40dB per decade after the cut-off frequency. The damped resonance frequency expressed in radiant of filter 20a is

$$\omega_{filter20u} = \sqrt{\frac{1}{L_{21}C_{21}} - \frac{R_{21}^{2}}{2L_{21}^{2}}}$$

(E4)

[0071] The output impedance of filter 20a is defined in accordance with the following

$$Z_{filter20a}(s) = \frac{R_{21} + s L_{21}}{1 + s C_{21} R_{21} + s^2 L_{21} C_{21}}$$

(E5)

and the transfer function of filter 20a is defined as

5

10

15

30

45

50

55

$$H_{filter20a}(s) = \frac{1}{1 + s R_{21} C_{21} + s^2 L_{21} C_{21}}$$

(E6)

[0072] Figure 7 illustrates the circuit diagram of differential low pass filter 20b exhibiting a passive second order RLC filter. In the description, the term resonant frequency corresponds to the undamped resonance or natural frequency  $\omega_0$  of an RLC circuit and damped resonance frequency is a frequency derived from the natural frequency and the damping factor of a RLC circuit.

[0073] As shown in Figure 7, the low pass filter20b configuration may receive a high voltage pulse modulated signal provided at input terminal IN22a with respect to a complemented high voltage pulse modulated signal provided at input terminal IN22b, wherein the filter 20b stage comprises a series connection of the first resistor R22a, the first inductor L22a, capacitor C22, the second inductor L22b and the second resistor R22b, the series connection connected between the first input terminal IN22a and the second input terminal IN22b. The constituted capacitor C22 in the low pass filter 20b configuration represents the capacitive load of an electrostatic speaker element.

[0074] The differential filter 20b setting exhibits the equivalent model of the single ended filter 20a setting, which is implemented in another form. In order to match the filter characteristics of both the single ended filter 20a setting and the differential filter 20b setting, the resistance of resistor R21 is divided by 2, and assigned to the resistors R22a and R22b. Furthermore the inductance of inductor L21 is divided by 2 and assigned to the inductors L22a and L22b, and finally the capacitance of capacitor C21 is equal to the capacitance of capacitor C22 representing the specified capacitive load.

[0075] In the case a single ended filter 20a setting is employed, one of the critical factors, involved in designing a stable functioning extraction filter, is the attenuation characteristics at the resonant frequency. In order to meet the optimum attenuation characteristics of a low pass filter 20a setting and subsequently the specified optimum damping requirement, the resonant frequency in radiant defined by equation E4 is set to zero, in which peaking of the attenuation characteristics at the resonant frequency will be obviated. The specified optimum damping requirement presents a well balanced condition, in which a filter 20a setting is just yet stable preventing perturbed behaviour and on the other hand preserving a minimum of attenuation in order to provide a low pass filter 20a setting with an operational bandwidth as wide and a frequency response as flat as possible.

**[0076]** If the damped resonance frequency  $\omega_d$  in radiant defined by equation E4 is set to zero, then equation E4 can be rewritten in more general terms in accordance with the following

$$\frac{R}{\sqrt{2}L} = \frac{1}{\sqrt{LC}} \tag{E7}$$

wherein R is the resistance, L is the inductance and C the capacitance.

[0077] Rearranging equation E7 may result in the following expression on the condition that the damped resonance frequency  $\omega_d$  in radiant defined by equation E4 is set to zero

$$\frac{\sqrt{2}}{RC} = \frac{1}{\sqrt{LC}} \tag{E8}$$

**[0078]** If equation E8 is solved for R, in which R is the optimum damping resistance value, then R can be expressed in accordance with the following

$$R = \sqrt{2} \sqrt{\frac{L}{C}}$$

(E9)

5

15

25

30

45

[0079] The quality factor Q of a damped second order filter as shown in the filter 20a setting can be defined in more general terms in accordance with the following

$$Q = \frac{\sqrt{\frac{L}{C}}}{R}$$

(E10)

[0080] Substituting expression E9 into expression E10 defining R, in which the damped resonance frequency will be set to zero as described above, and solved for Q, than Q is equal to the following result

$$Q = \frac{1}{\sqrt{2}} \tag{E11}$$

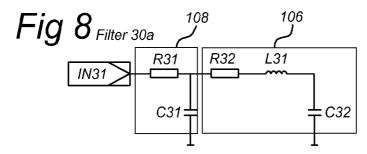

**[0081]** Figure 8 illustrates the circuit diagram of single ended extraction filter 30a, which exhibits a passive low pass third order filter, constituted of a second filter stage and a first filter stage. The second filter stage comprises a RC filter and the first filter stage comprises a RLC circuit. The component value setting of extraction filter 30a and subsequently the derived differential filter 30b setting as described hereinafter will be implemented from the point of view of sufficiently damping the signal component at the resonant frequency emanated from the under damped first filter stage by means of the constituted damping components resided in the second filter stage.

[0082] As shown in Figure 8, the low pass filter 30a configuration may receive a high voltage pulse modulated signal provided at input terminal IN31 with respect to ground, wherein a second filter stage of filter 30a comprises a series connection of a second stage resistor R31 and a second stage capacitor C31, the series connection connected between a second stage input terminal IN31 and a ground node, and wherein a first filter stage of filter 30a comprises a series connection of a first stage resistor R32, a first stage inductor L31 and a first stage capacitor C32, the series connection connected between the second stage input terminal and a ground node, a node between the second stage resistor R31 and the second stage capacitor C31 is coupled to an output node of the second filter stage, the output node is coupled to the first stage input terminal of the first filter stage. The constituted first stage capacitor C32 in the low pass filter 30a configuration represents the capacitive load of an electrostatic speaker element.

[0083] Ideally the roll-off of the low pass third order filter 30a setting provides an attenuation of 60dB per decade after the second cut-off frequency. The output impedance of filter 30a is defined in accordance with the following

$$Z_{filter30a}(s) = \frac{R_{31} + R_{32} + s L_{31} + s R_{31} R_{32} C_{31} + s^2 R_{31} L_{31} C_{31}}{1 + s R_{31} C_{31} + s R_{31} C_{32} + s R_{32} C_{32} + s^2 R_{31} R_{32} C_{31} C_{32} + s^2 L_{31} C_{32} + s^3 R_{31} L_{31} C_{32} C_{31}}$$

(E12)

and the transfer function of filter 30a is defined as

30

35

45

50

$$H_{filter30a}(s) = \frac{1}{1 + s R_{31} C_{31} + s R_{31} C_{32} + s R_{32} C_{32} + s^2 R_{31} R_{32} C_{31} C_{32} + s^2 L_{31} C_{32} + s^3 R_{31} L_{31} C_{32} C_{31}}$$

10 (E13)

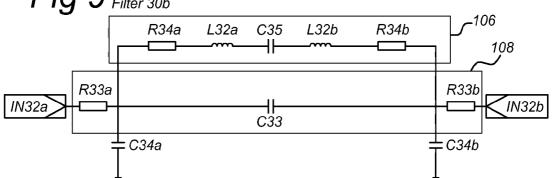

[0084] Figure 9 illustrates the circuit diagram of differential extraction filter 30b, which exhibits a passive low pass third order filter.

[0085] As shown in Figure 9, the low pass filter30b configuration may receive a high voltage pulse modulated signal provided at input terminal IN32a with respect to a complemented high voltage pulse modulated signal provided at input terminal IN32b, wherein a second filter stage of filter 30b comprises a series connection of a first second stage resistor R33a, a second stage capacitor C33 and a second second stage resistor R33b, the series connection connected between the first second stage input terminal IN32a and the second second stage input terminal IN32b, a first filter stage of filter 30b stage comprises a series connection of a first first stage resistor R34a, a first first stage inductor L32a, a first stage capacitor C35, a second first stage inductor L32b and a second first stage resistor R34b, the series connection connected between a first first stage terminal and a second first stage terminal, a node between the first second stage resistor R33a and the second stage capacitor C33 is coupled to a first output node of the second filter stage of filter 30b and a node between the second second stage resistor R33b and the second stage capacitor C33 is coupled to a second output node of the second filter stage, the first output node of the second filter stage is coupled to the first first stage terminal and the second output node of the second filter stage is coupled to the second filter stage terminal, furthermore the capacitor C34a is connected between the first output node and a ground node, the capacitor C34b is connected between the second output node and a ground node. The constituted first stage capacitor C35 in the low pass filter 30b configuration represents the capacitive load of an electrostatic speaker element.

**[0086]** The differential filter 30b setting excluding the capacitors C34a and C34b exhibits the equivalent model of the single ended filter 30a setting, which is implemented in another form.

[0087] Similarly the differential filter 30b setting excluding capacitor C33 exhibits the equivalent model of the single ended filter 30a setting as well. Subsequently the differential low pass filter 30b configuration may be implemented by means of a single capacitor C33 excluding the capacitors C34a and C34b, which forms the preferred configuration, by means of the capacitors C34a and C34b referenced to a DC voltage or ground node excluding capacitor C33 or by means of a combination of the capacitors C33, C34a and C34b. In order to match the filter characteristics of both the single ended filter 30a setting and the differential filter 30b setting, the resistance of resistor R31 is divided by 2 and assigned to the resistors R34a and R34b, furthermore the inductance of inductor L31 is divided by 2 and assigned to the inductors L32a and L32b. In the case capacitor C33 is implemented excluding the capacitors C34a and C34b, than the capacitance of capacitor C31 is equal to the capacitance of capacitor C33. Implementing the capacitors C34a and C34b in the low pass differential filter 30a configuration excluding capacitor C33, than the capacitance of capacitor C31 is multiplied by 2 and assigned to the capacitors C34a and C34b. Finally the capacitance of capacitor C32 is equal to the capacitance of capacitor C35 representing the specified capacitive load.

[0088] In the case a single ended filter 30a setting is employed, one of the critical factors, involved in designing a stable functioning filter, is to obtain the proper ratio between the capacitance values of capacitor C31 and capacitor C32 in conjunction with the proper damping resistance of the resistors R31 and R32 in order to meet the optimum attenuation characteristics. In order to obtain the optimum low pass filter 30a setting with an operational bandwidth as wide and a frequency response as flat as possible, it is desired to eliminate resistor R32 in the filter 30a configuration. However, due to the practical limitations of inductor L31 a small resistance value will remain, in which resistor R32 may represent the internal DC resistance of inductor L31. As a result the low pass filter 30a configuration becomes a good approximation to the optimum low pass filter 30a setting. Therefore, without compromising the results, resistor R32 constituted in the low pass filter 30a configuration will be ignored in the following equations and descriptions disclosed until further notice.

[0089] In order to meet the optimum damping requirement the resistance value of resistor R31 is set equal to the characteristic impedance of the RLC circuit comprising inductor L31 and capacitor C32 in conjunction with capacitor C31 as can be expressed in accordance with the following

$$R_{31} = \sqrt{\frac{L_{31}}{C_{32} - \frac{C_{31}C_s}{C_{31} + C_{32}}}}$$

(E14)

wherein the capacitance value Cs represents the equivalent value of capacitor C31 series connected to capacitor C32 as can be expressed as

$$C_s = \frac{C_{31} C_{32}}{C_{31} + C_{32}} \tag{E15}$$

[0090] The proper ratio between the capacitance values of capacitor C31 and capacitor C32 can be obtained by means of equation E8, in which equation E8 may be rewritten in order to meet the low pass filter 30a setting according to the following equation

$$\frac{\sqrt{2}}{R_{31}(C_{31} + C_{32})} = \frac{1}{\sqrt{L_{31}C_{32}}}$$

(E16)

[0091] If the proper ratio between the capacitance values of capacitor C31 and capacitor C32 is expressed in a ratio factor *n* than the capacitance value of capacitor C32 may be set equal to the following expression

$$C_{32} = n C_{31} (E17)$$

[0092] Substituting expression E14 and E17 into equation E16 results in the following equation

$$\frac{\frac{\sqrt{2}}{L_{31}}}{n C_{31} - \frac{C_{31} n C_{31}}{C_{31} + n C_{31}}} (C_{31} + n C_{31}) = \frac{1}{\sqrt{L_{31} n C_{31}}}$$

(E18)

**[0093]** If equation E18 is solved for n, in which n is the optimal ratio factor in conjunction with the optimal damping resistance resided in expression E14 as described above, than n is equal to the following rounded result

$$n = 2.7540 (E19)$$

and subsequently expression E17 can be written as

5

10

30

35

40

50

55

$$C_{32} = 2.7540 \ C_{31} \tag{E20}$$

**[0094]** In order to obtain the desired impulse response of the filter 30a setting, the quality factor Q may be adjusted by means of resistor R32 yielding a lower quality factor Q with increasing resistance of resistor R32. The relationship between the resistance of resistor R32 and the quality factor Q can be expressed in accordance with the following

$$R_{32} = \left(\frac{1}{Q} - \sqrt{2}\right) \sqrt{\frac{L_{31}}{C_{32}}} \qquad \{Q \le \frac{1}{\sqrt{2}}\}$$

(E21)

**[0095]** The single ended filter 30a setting and the equivalent differential filter 30b setting provide an approach that allows a stable extraction filter obtaining a wider operational bandwidth with a flat frequency response in conjunction with improved roll-off characteristics with respect to the above described extraction filter embodiments.

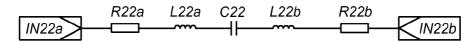

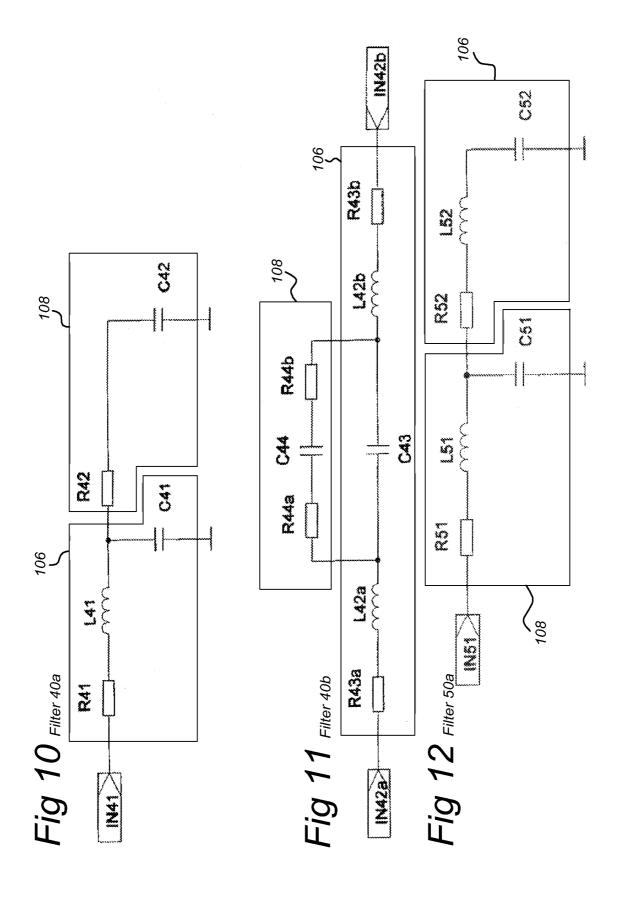

**[0096]** Figure 10 illustrates the circuit diagram of single ended extraction filter 40a, which exhibits a passive low pass third order filter, constituted of a first filter stage and a second filter stage. The first filter stage comprising a RLC circuit and the second filter stage comprising a RC circuit. The component value setting of extraction filter 40a and subsequently the derived differential filter 40b setting as described hereinafter will be implemented from the point of view of damping the signal component at the resonant frequency emanated from the under damped first filter stage by means of the constituted damping components resided in the second filter stage.

[0097] As shown in Figure 10, the low pass filter 40a configuration may receive a high voltage pulse modulated signal provided at input terminal IN41 with respect to ground, wherein a first filter stage 106 of filter 40a comprises a series connection of a first stage resistor R41, a first stage inductor L41 and a first stage capacitor C41, the series connection connected between a first stage input terminal IN41 and a ground node, and wherein the second filter stage of filter 40a comprises a series connection of a second stage resistor R42 and a second stage capacitor C42, the series connection connected between a second stage input terminal and a ground node, a node between the first stage inductor L41 and the first stage capacitor C41 is coupled to an output node of the first filter stage, the output node is coupled to the second stage input terminal of the second filter stage. The constituted second stage capacitor C42 in the low pass filter 40a configuration represents the capacitive load of an electrostatic speaker element.

[0098] Ideally the roll-off of the low pass third order filter 40a setting provides an attenuation of 60dB per decade after the second cut-off frequency. The output function of filter 40a is defined in accordance with the following

$$Z_{filter40a}(s)$$

$(R_{41} + R_{42} + s L_{41} + s R_{41} R_{42} C_{41} + s^2 R_{42} L_{41} C_{41})$   $(1 + s R_{41} C_{41} + s R_{41} C_{42} + s R_{41} C_{42} + s^2 R_{41} R_{42} C_{41} C_{42} + s^2 L_{41} C_{41} + s^2 L_{41} C_{42} + s^3 R_{42} L_{41} C_{41} C_{42})$  (E22)

and the transfer function of filter 40a is defined as

$$H_{filter \neq 0a}(s) =$$

30

35

50

$$1/(1 + s R_{41} C_{41} + s R_{41} C_{42} + s R_{42} C_{42} + s^2 R_{41} R_{42} C_{41} C_{42} + s^2 L_{41} C_{41} + s^2 L_{41} C_{42} + s^3 R_{42} L_{41} C_{41} C_{42})$$

(E23)

**[0099]** Figure 11 illustrates the circuit diagram of differential extraction filter 40b, which exhibits a passive low pass third order filter.

**[0100]** As shown in Figure 11, the low pass filter40b configuration may receive a high voltage pulse modulated signal provided at input terminal IN42a with respect to a complemented high voltage pulse modulated signal provided at input terminal IN42b, wherein a first filter stage 106 of filter 40b comprises a series connection of a first first stage resistor R43a, a first first stage inductor L42a, a first stage capacitor C43, a second first stage inductor L42b and a second first stage resistor R43b, the series connection connected between a first first stage input terminal IN42a and a second first stage input terminal IN42b, a second filter stage of filter 40b stage comprises a series connection of a first second stage

resistor R44a, a second stage capacitor C44 and a second second stage resistor R44b, the series connection connected between a first second stage input terminal and a second second stage input terminal, a node between the first first stage inductor L42a and the first stage capacitor C43 is coupled to a first output node of the first filter stage 106 and a node between the second first stage inductor L42b and the first stage capacitor C43 is coupled to a second output node of the first filter stage 106, the first output node is coupled to the first second stage input terminal and the second output node is coupled to the second second stage input terminal. The constituted second stage capacitor C44 in the low pass filter 40b configuration represents the capacitive load of an electrostatic speaker element.

**[0101]** The differential filter 40b setting exhibits the equivalent model of the single ended filter 40a setting, which is implemented in another form. In order to match the filter characteristics of both the single ended filter 40a setting and the differential filter 40b setting, the resistance of resistor R41 is divided by 2 and assigned to the resistors R43a and R43b, the resistance of resistor R42 is divided by 2 and assigned to the resistors R44a and R44b, furthermore the inductance of inductor L41 is divided by 2 and assigned to the inductors L42a and L42b, the capacitance of capacitor C43 is equal to the capacitance of capacitor C41 and finally the capacitance of capacitor C42 is equal to the capacitance of capacitor C44 representing the specified capacitive load.

10

50

[0102] In the case a single ended filter 40a setting is employed, it is emphasised to obtain the proper ratio between the capacitance values of capacitor C41 and capacitor C42 in conjunction with the proper damping resistance of the resistors R41 and R42 in order to meet the optimum attenuation characteristics. In order to obtain the optimum low pass filter 40a setting with an operational bandwidth as wide and a frequency response as flat as possible, it is desired to eliminate resistor R41 in the extraction filter 40a configuration. However, due to the practical limitations of inductor L41 a small resistance value will remain, in which resistor R41 may represent the internal DC resistance of inductor L41. As a result the low pass filter 40a configuration becomes a good approximation to the optimum low pass filter 40a setting. Therefore, without compromising the results, resistor R41 constituted in the low pass filter 40a configuration will be ignored in the following equations and descriptions disclosed until further notice.

In order to meet the optimum damping requirement the resistance value of resistor R42 is set equal to the characteristic impedance of the RLC circuit comprising inductor L41 and capacitor C41 as can be expressed in accordance with the following

$$R_{42} = \sqrt{\frac{L_{41}}{C_{41}}}$$

(E24)

<sup>35</sup> **[0103]** The proper ratio between the capacitance values of capacitor C41 and capacitor C42 can be obtained by means of equation E8, in which equation E8 may be rewritten in order to meet the low pass filter 40a setting according to the following equation

$$\frac{\sqrt{2}}{R_{42}C_{42}} = \frac{1}{\sqrt{L_{41}(C_{41} + C_{42})}}$$

(E25)

[0104] If the proper ratio between the capacitance values of capacitor C41 and capacitor C42 is expressed in a ratio factor *n*, than the capacitance value of capacitor C42 may be set equal to the following expression

$$C_{42} = n C_{41}$$

(E26)

[0105] Substituting expression E24 and E26 into equation E25 results in the following equation

$$\frac{\sqrt{2}}{\sqrt{\frac{L_{41}}{C_{41}}} n C_{41}} = \frac{1}{\sqrt{L_{41} (C_{41} + n C_{41})}}$$

(E27)

If equation E27 is solved for n, in which n is the optimal ratio factor in conjunction with the optimal damping resistance resided in expression E24 as described above, than n is equal to the following result

$$n = 1 + \sqrt{3} \tag{E28}$$

and subsequently expression E26 can be written as

5

15

20

30

35

45

50

55

$$C_{42} = (1 + \sqrt{3}) C_{41}$$

(E29)

**[0106]** In order to obtain the desired impulse response of the filter 40a setting, the quality factor Q may be adjusted by means of resistor R41 yielding a lower quality factor Q with increasing resistance of resistor R41. The relationship between the resistance of resistor R41 and the quality factor Q can be expressed in accordance with the following

$$R_{41} = \left(\frac{1}{Q} - \sqrt{2}\right) \sqrt{\frac{L_{41}}{C_{41} + C_{42}}} \qquad \{Q \le \frac{1}{\sqrt{2}}\}$$

(E30)

**[0107]** The single ended filter 40a setting and the equivalent differential filter 40b setting provide an approach that allows a stable extraction filter obtaining a wide operational bandwidth with a flat frequency response and roll-off characteristics comparable to the single ended filter 30a and differential filter 30b embodiments. It is to be noted that in filter 40a and filter 40b less power will be dissipated by the resistors of the extraction filter as the high frequencies in the signal supplied to the resistor are attenuated obtaining high efficiency with respect to the above described filter embodiments shown in figures 4 - 9. In filter 40a and filter 40b less power will be dissipated by the resistors of the extraction filter as the high frequencies in the signal supplied to the resistor are attenuated.

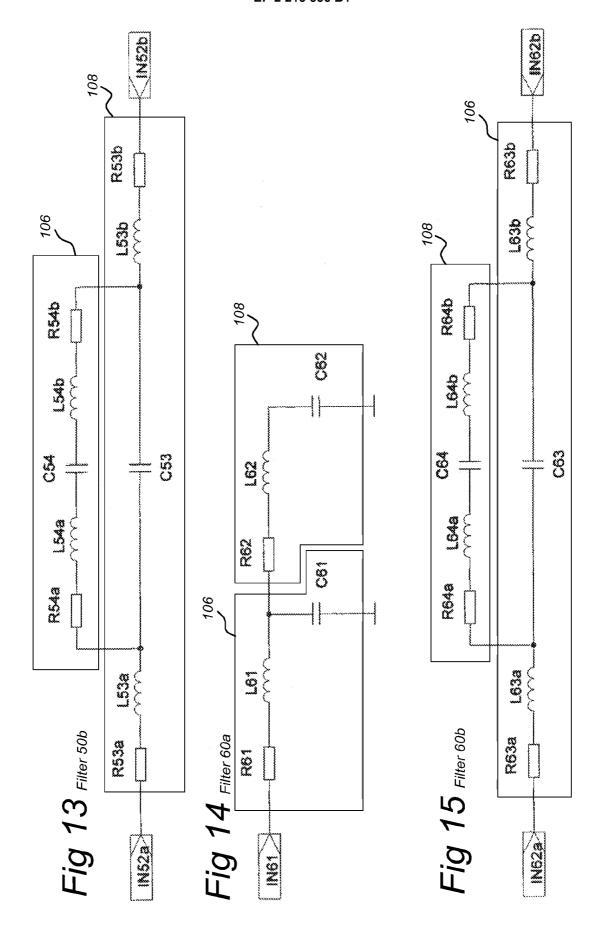

[0108] Figure 12 illustrates the circuit diagram of single ended extraction filter 50a, which exhibits a passive low pass fourth order filter, constituted of a first RLC filter stage 106 and a second RLC filter stage 108, wherein the component value setting of extraction filter 50a and subsequently the derived differential filter50b setting as described hereinafter will be implemented from the point of view of damping the signal component at the resonant frequency emanated from the under damped first filter stage by means of the constituted damping components resided in the second filter stage.

[0109] As shown in Figure 12, the low pass filter 50a configuration may receive a high voltage pulse modulated signal provided at input terminal IN51 with respect to ground, wherein a first second stage 108 of filter 50a comprises a series connection of a second stage resistor R51, a second stage inductor L51 and a second stage capacitor C51, the series connection connected between input terminal IN51 and a ground node, and wherein a first filter stage of filter 50a comprises a series connection connected between a first stage resistor R52, a first stage inductor L52 and a first stage capacitor C52, the series connection connected between a first stage input terminal and a ground node, a node between the second stage inductor L51 and the second stage capacitor C51 is coupled to the output node of the second filter stage 108, the output node is coupled to the first stage input terminal of the first filter stage 106. The constituted first stage capacitor C52 in the low pass filter 50a configuration represents the capacitive load of an electrostatic speaker element.

**[0110]** Ideally the roll-off of the low pass fourth order filter 50a setting provides an attenuation of 80dB per decade after the second cut-off frequency. The output function of filter 50a is defined in accordance with the following

$$Z_{filter 50a}(s)$$

5

15

20

30

35

50

$$(R_{51} + R_{52} + s L_{51} + s L_{52} + s R_{51} R_{52} C_{51} + s^2 R_{52} L_{51} C_{51} + s^2 R_{51} L_{52} C_{51} + s^3 L_{51} L_{52} C_{51})$$

$$(1 + s R_{51} C_{51} + s R_{51} C_{52} + s R_{52} C_{52} + s^2 R_{51} R_{52} C_{51} C_{52} + s^2 L_{51} C_{51}$$

$$+ s^2 L_{51} C_{52} + s^2 L_{52} C_{52} + s^3 R_{52} L_{51} C_{51} C_{52} + s^3 R_{51} L_{52} C_{51} C_{52} + s^4 L_{51} L_{52} C_{51} C_{52})$$

(E31)

and the transfer function of filter 50a is defined as

$$H_{filter 50a}(s)$$

$1/(1+sR_{51}C_{51}+sR_{51}C_{52}+sR_{52}C_{52}+s^2R_{51}R_{52}C_{51}C_{52}+s^2L_{51}C_{51}+s^2L_{51}C_{52}$   $+s^2L_{52}C_{52}+s^3R_{52}L_{51}C_{51}C_{52}+s^3R_{51}L_{52}C_{51}C_{52}+s^4L_{51}L_{52}C_{51}C_{52})$

(E32)

**[0111]** Figure 13 illustrates the circuit diagram of differential extraction filter 50b, which exhibits a passive low pass fourth order filter.

**[0112]** As shown in Figure 13, the low pass filter50b configuration may receive a high voltage pulse modulated signal provided at first input terminal IN52a with respect to a complemented high voltage pulse modulated signal provided at second input terminal IN52b, wherein a second filter stage 108 of filter 50b comprises a series connection of a first second stage resistor R53a, a first second stage inductor L53a, a second stage capacitor C53, a second second stage inductor L53b and a second second stage resistor R53b, the series connection connected between a first input terminal IN52a and a second input terminal IN52b, a first filter stage 106 of filter 50b comprises a series connection of a first first stage resistor R54a, a first first stage capacitor C54, a second first stage inductor L54b and a second first stage resistor R54b, the series connection connected between a first first stage input terminal and a second first stage input terminal, a node between the first second stage inductor L53a and the second stage capacitor C53 is coupled to a first output node of the second filter stage 108 and a node between the second stage inductor L53b and the second stage capacitor C53 is coupled to a second output node is coupled to the first first stage input terminal and the second output node is coupled to the second first stage input terminal. The constituted first stage capacitor C54 in the low pass filter 50b configuration may represent the capacitive load of an electrostatic speaker element.

**[0113]** The differential filter 50b setting exhibits the equivalent model of the single ended filter 50a setting, which is implemented in another form. In order to match the filter characteristics of both the single ended filter 50a setting and the differential filter 50b setting, the resistance of resistor R51 is divided by 2 and assigned to the resistors R53a and R53b, the resistance of resistor R52 is divided by 2 and assigned to the resistors R54a and R54b, furthermore the inductance of inductor L51 is divided by 2 and assigned to the inductors L53a and L53b, the inductance of inductor L52 is divided by 2 and assigned to the inductors L54a and L54b, the capacitance of capacitor C53 is equal to the capacitance of capacitor C51 and finally the capacitance of capacitor C52 is equal to the capacitance of capacitor C54 representing the specified capacitive load.

**[0114]** In case a single ended filter 50a setting is employed, it is emphasised to obtain a first ratio between the capacitance values of capacitor C51 and capacitor C52 and a second ratio between the inductance values of inductor L51 and inductor L52, in which the first and second proper ratios in conjunction with the proper damping resistance of the resistors R51 and R52 will meet the optimum attenuation characteristics. In order to obtain the optimum low pass filter 50a setting with an operational bandwidth as wide and a frequency response as flat as possible, it is desired to eliminate resistor R52 in the extraction filter 50a configuration. However, due to the practical limitations of inductor L52

a small resistance value will remain, in which resistor R52 may represent the internal DC resistance of inductor L52. As a result the low pass filter 50a configuration becomes a good approximation to the optimum low pass filter 50a setting. Therefore, without compromising the results, resistor R52 constituted in the low pass filter 50a configuration will be ignored in the following equations and descriptions disclosed until further notice.

[0115] In order to meet the optimum damping requirement the resistance value of resistor R51 is set equal to the characteristic impedance of the first stage RLC circuit comprising inductor L51 and capacitor C51 in conjunction with quality factor Q51 in order to set the damping of the first stage RLC circuit, and the characteristic impedance of the second stage RLC circuit comprising inductor L52 in conjunction with the capacitors C51 and C52 as can be expressed in accordance with the following

$$R_{51} = \sqrt{\frac{L_{51}}{Q_{51}^{2}(C_{51} + C_{52})} + \frac{L_{52}}{C_{52} - \frac{C_{51}C_{s}}{C_{51} + C_{52}}}}$$

{0 < Q<sub>51</sub>}

wherein the capacitance value Cs represents the equivalent value of capacitor C51 series connected to capacitor C52 as can be expressed as

$$C_s = \frac{C_{51} C_{52}}{C_{51} + C_{52}} \tag{E34}$$

**[0116]** The proper ratios between the constituted capacitor and inductor values can be obtained by means of equation E8, in which equation E8 may be rewritten in order to meet the single ended filter 50a setting according to the following equation

$$\frac{\sqrt{2}}{R_{51} (C_{51} + C_{52})} = \frac{1}{\sqrt{L_{51} (C_{51} + C_{52}) + L_{52} C_{52}}}$$

(E35)

**[0117]** If the proper ratios between the constituted capacitor and inductor values are expressed in the ratio factors n and m, than the capacitance value of capacitor C52 and the inductance value of inductor L52 may be set equal to the following expressions

$$C_{52} = n C_{51} \tag{E36}$$

and

10

15

20

25

30

35

40

45

50

55

$$L_{52} = n \, m \, L_{51} \tag{E37}$$

[0118] Substituting expression E33, E36 and E37 into equation E35 results in the following equation

$$\frac{\sqrt{2}}{Q_{51}^{2}(C_{51}+nC_{51})} + \frac{n m L_{51}}{C_{51} \frac{C_{51} n C_{51}}{C_{51} + n C_{51}}} (C_{51}+nC_{51})$$

$$n C_{51} - \frac{C_{51} \frac{C_{51} n C_{51}}{C_{51} + n C_{51}}}{C_{51} + n C_{51}}$$